21264/EV68A Hardware Reference Manual

Cache and External Interfaces 4–9

Cache Coherency

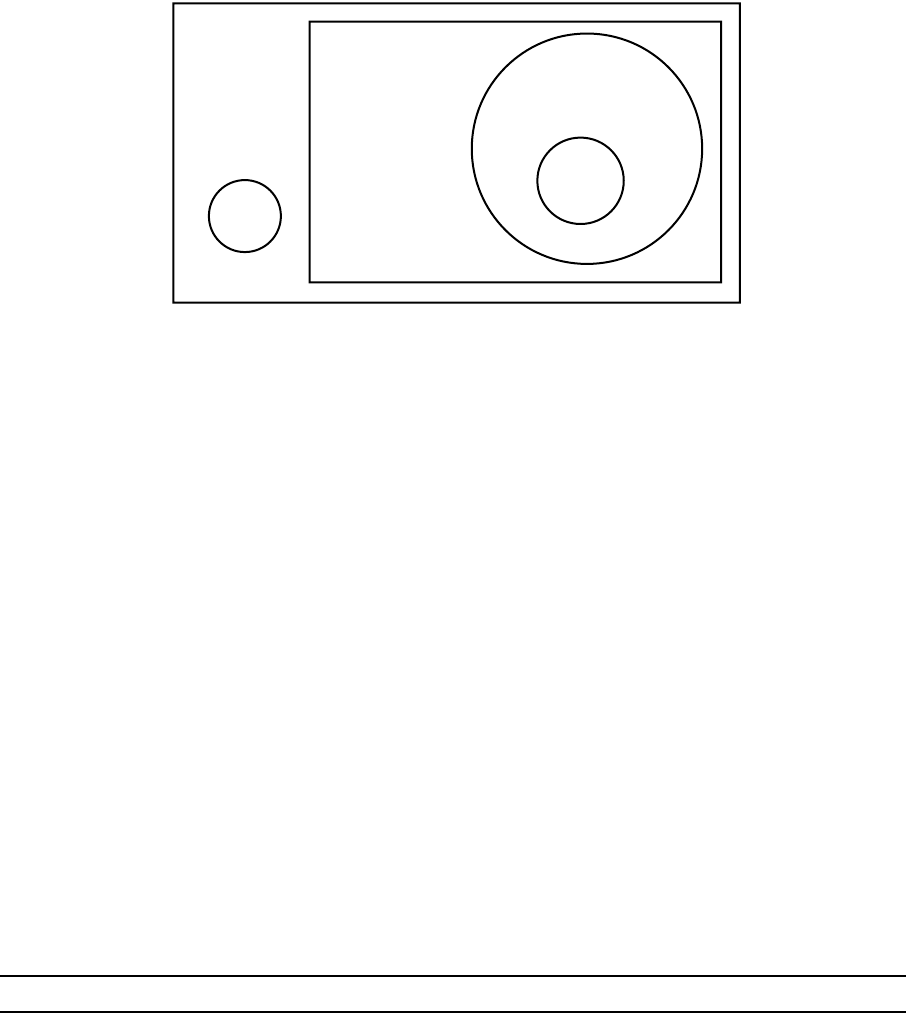

Figure 4–3 Cache Subset Hierarchy

The following tasks must be performed to maintain cache coherency:

• Istream data from memory spaces may be cached in the Icache and Bcache. Icache

coherence is not maintained by hardware—it must be maintained by software using

the CALL_PAL IMB instruction.

• The 21264/EV68A maintains the Dcache as a subset of the Bcache. The Dcache is

set-associative but is kept a subset of the larger externally implemented direct-

mapped Bcache.

• System logic must help the 21264/EV68A to keep the Bcache coherent with main

memory and other caches in the system.

• The 21264/EV68A requires the system to allow only one change to a block at a

time. This means that if the 21264/EV68A gains the bus to read or write a block, no

other node on the bus should be allowed to access that block until the data has been

moved.

• The 21264/EV68A provides hardware mechanisms to support several cache coher-

ency protocols. The protocols can be separated into two classes: write invalidate

cache coherency protocol and flush cache coherency protocol.

4.5.2 Cache Block States

Table 4–2 lists the cache block states supported by the 21264/EV68A.

Table 4–2 21264/EV68A-Supported Cache Block States

State Name Description

Invalid The 21264/EV68A does not have a copy of the block.

Clean This 21264/EV68A holds a read-only copy of the block, and no other agent in the system

holds a copy. Upon eviction, the block is not written to memory.

System

Main Memory

Icache

Bcache

Dcache

FM-05824.AI4