21264/EV68A Hardware Reference Manual

Internal Processor Registers 5–9

Ibox IPRs

5.2.8 Instruction Virtual Address Format Register — IVA_FORM

The instruction virtual address format register (IVA_FORM) is a read-only register. It

contains the virtual PTE address derived from the faulting virtual address stored in the

EXC_ADDR register, and from the virtual page table base, VA_48 and VA_FORM_32

bits, stored in the I_CTL register.

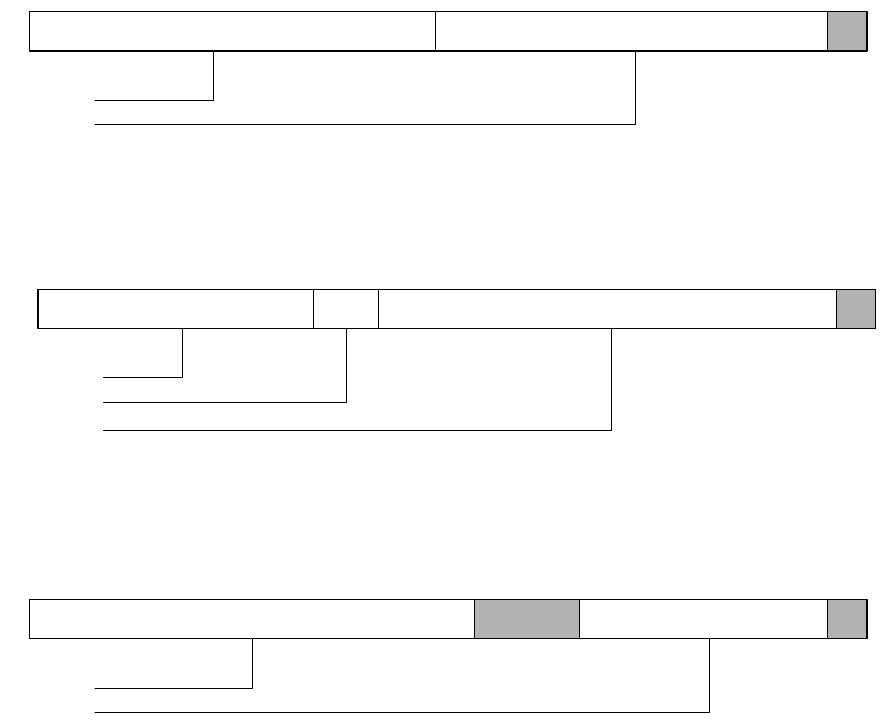

Figure 5–13 shows IVA_FORM when I_CTL(VA_48) equals 0 and

I_CTL(VA_FORM_32) equals 0.

Figure 5–13 Instruction Virtual Address Format Register (VA_48 = 0, VA_FORM_32 = 0)

Figure 5–14 shows IVA_FORM when I_CTL(VA_48) equals 1 and

I_CTL(VA_FORM_32) equals 0.

Figure 5–14 Instruction Virtual Address Format Register (VA_48 = 1, VA_FORM_32 = 0)

Figure 5–15 shows IVA_FORM when I_CTL(VA_48) equals 0 and

I_CTL(VA_FORM_32) equals 1.

Figure 5–15 Instruction Virtual Address Format Register (VA_48 = 0, VA_FORM_32 = 1)

5.2.9 Interrupt Enable and Current Processor Mode Register – IER_CM

The interrupt enable and current processor mode register (IER_CM) contains the inter-

rupt enable and current processor mode bit fields. These bit fields can be written either

individually or together with a single HW_MTPR instruction. When bits [7:2] of the

IPR index field of a HW_MTPR instruction contain the value 000010

2

, this register is

selected. Bits [1:0] of the IPR index indicate which bit fields are to be written: bit[1]

corresponds to the IER field and bit[0] corresponds to the processor mode field. A

HW_MFPR instruction to this register returns the values in both fields. Figure 5–16

shows the interrupt enable and current processor mode register.

63 33 332 20

VPTB[63:33]

VA[42:13]

LK

99

-

00

1

9

A

63 38 3743 342 20

VPTB[63:43]

SEXT(VA[47])

VA[47:13]

LK

99

-

00

2

0

A

63 29 322 22130 0

VPTB[63:30]

VA[31:13]

LK

99

-

00

21A