21264/EV68A Hardware Reference Manual

Internal Processor Registers 5–19

Ibox IPRs

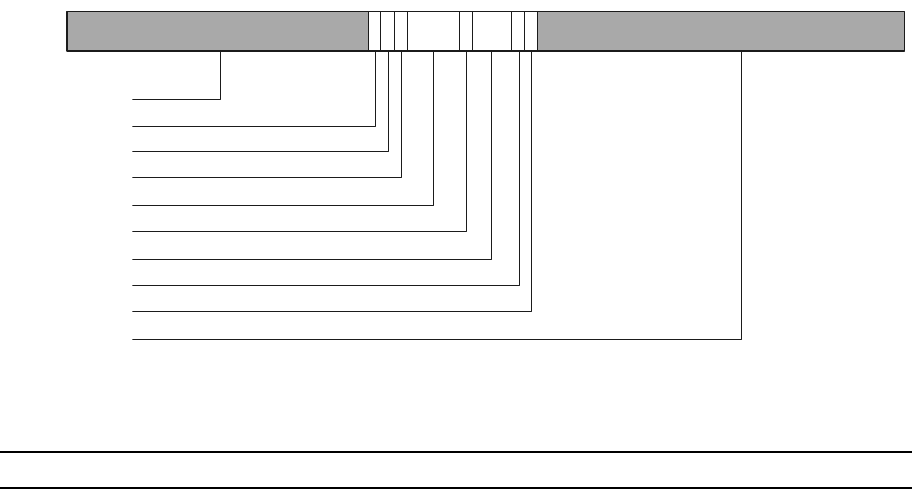

Figure 5–23 Ibox Status Register

Table 5–12 describes the Ibox status register fields.

Table 5–12 Ibox Status Register Fields Description

Name Extent Type Description

Reserved [63:41] RO Reserved for COMPAQ.

MIS [40] RO ProfileMe Mispredict Trap.

If the I_STAT[TRP] bit is set, this bit indicates that the profiled instruc-

tion caused a mispredict trap. JSR/JMP/RET/COR or HW_JSR/

HW_JMP/HW_RET/HW_COR mispredicts do not set this bit but can be

recognized by the presence of one of these instructions at the PMPC loca-

tion with the I_STAT[TRP] bit set. This identification is exact in all cases

except error condition traps. Hardware corrected Icache parity or Dcache

ECC errors, and machine check traps can occur on any instruction in the

pipeline.

TRP [39] RO ProfileMe Trap.

This bit indicates that the profiled instruction caused a trap. The trap type

field, PMPC register, and instruction at the PMPC location are needed to

distinguish all trap types.

LS0 [38] RO ProfileMe Load-Store Order Trap.

If the profiled instruction caused a replay trap, this bit indicates that the

precise trap cause was an Mbox load-store order replay trap.

If clear, this bit indicates that the replay trap was any one of the follow-

ing:

Mbox load-load order

Mbox load queue full

Mbox store queue full

Mbox wrong size trap (such as, STL → LDQ)

Mbox Bcache alias (2 physical addresses map to same Bcache line)

Mbox Dcache alias (2 physical addresses map to same Dcache line)

Icache parity error

Dcache ECC error

63 39 2938 282737 3433324140 30 0

Reserved

MIS

TRP

LS0

TRAP TYPE[3:0]

ICM

OVR[2:0]

PAR

LAM

Reserved

LK

99

-

003

1A