5–16 Internal Processor Registers

21264/EV68A Hardware Reference Manual

Ibox IPRs

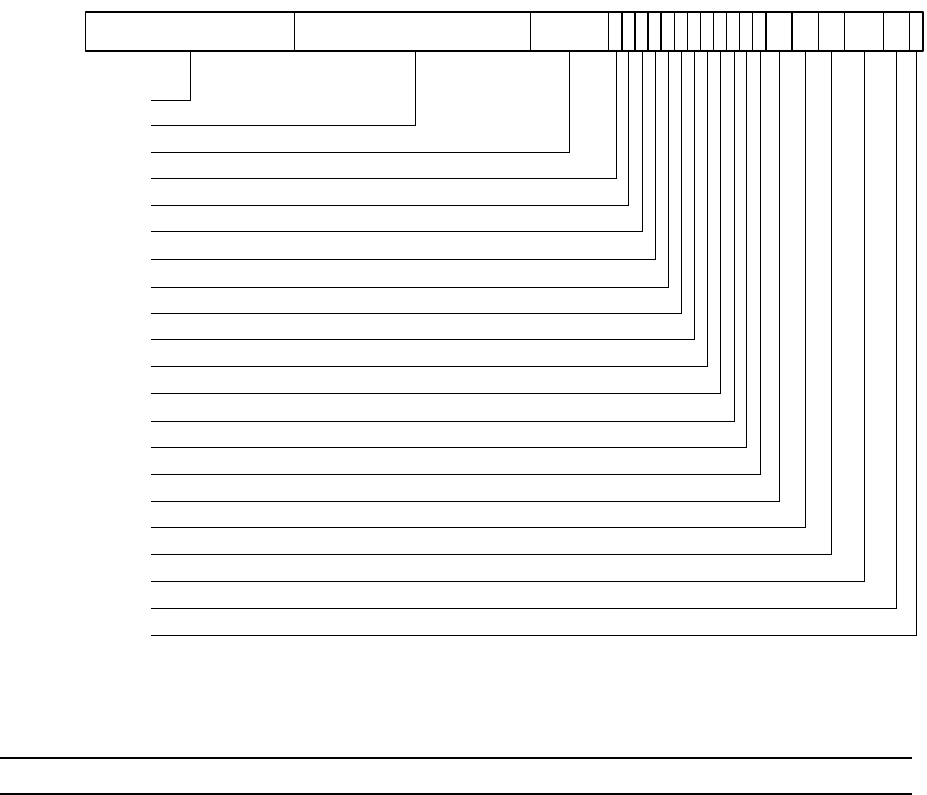

Figure 5–22 Ibox Control Register

Table 5–11 describes the Ibox control register fields.

Table 5–11 Ibox Control Register Fields Description

Name Extent Type Description

SEXT(VPTB[47]) [63:48] RW,0 Sign extended VPTB[47].

VPTB[47:30] [47:30] RW,0 Virtual Page Table Base. See Section 5.1.5 for details.

CHIP_ID[5:0] [29:24] RO This is a read-only field that supplies the revision ID number

for the 21264/EV68A part.

21264/EV68A pass 2.1 ID is 010010

2

.

BIST_FAIL [23] RO,0 Indicates the status of BiST (clear = pass, set = fail),

described in Section 11.5.1.

TB_MB_EN [22] RW,0 When set, the hardware ensures that the virtual-mode loads

in DTB and ITB fill flows that access the page table and the

subsequent virtual mode load or store that is being retried are

‘ordered’ relative to another processor’s stores. This must be

set for multiprocessor systems in which no MB instruction is

present in the TB fill flow, unless there are other mecha-

nisms present that ensure coherency.

MCHK_EN [21] RW,0 Machine check enable — set to enable machine checks.

SEXT(VPTB[47])

VPTB[47:30]

CHIP_ID[5:0]

BIST_FAIL

TB_MB_EN

MCHK_EN

ST_WAIT_64K

PCT1_EN

PCT0_EN

SINGLE_ISSUE_H

VA_FORM_32

VA_48

SL_RCV

HWE

BP_MODE[1:0]

SBE[1:0]

SDE[1:0]

SPE[2:0]

IC_EN[1:0]

SPCE

SL_XMIT

63 29 19 948 18 847 17 716 615 524 1423 13 322 12 221 11 130 20 10 0

LK

99

-

00

2

9

A