5–12 Internal Processor Registers

21264/EV68A Hardware Reference Manual

Ibox IPRs

Table 5–7 describes the interrupt summary register fields.

5.2.12 Hardware Interrupt Clear Register – HW_INT_CLR

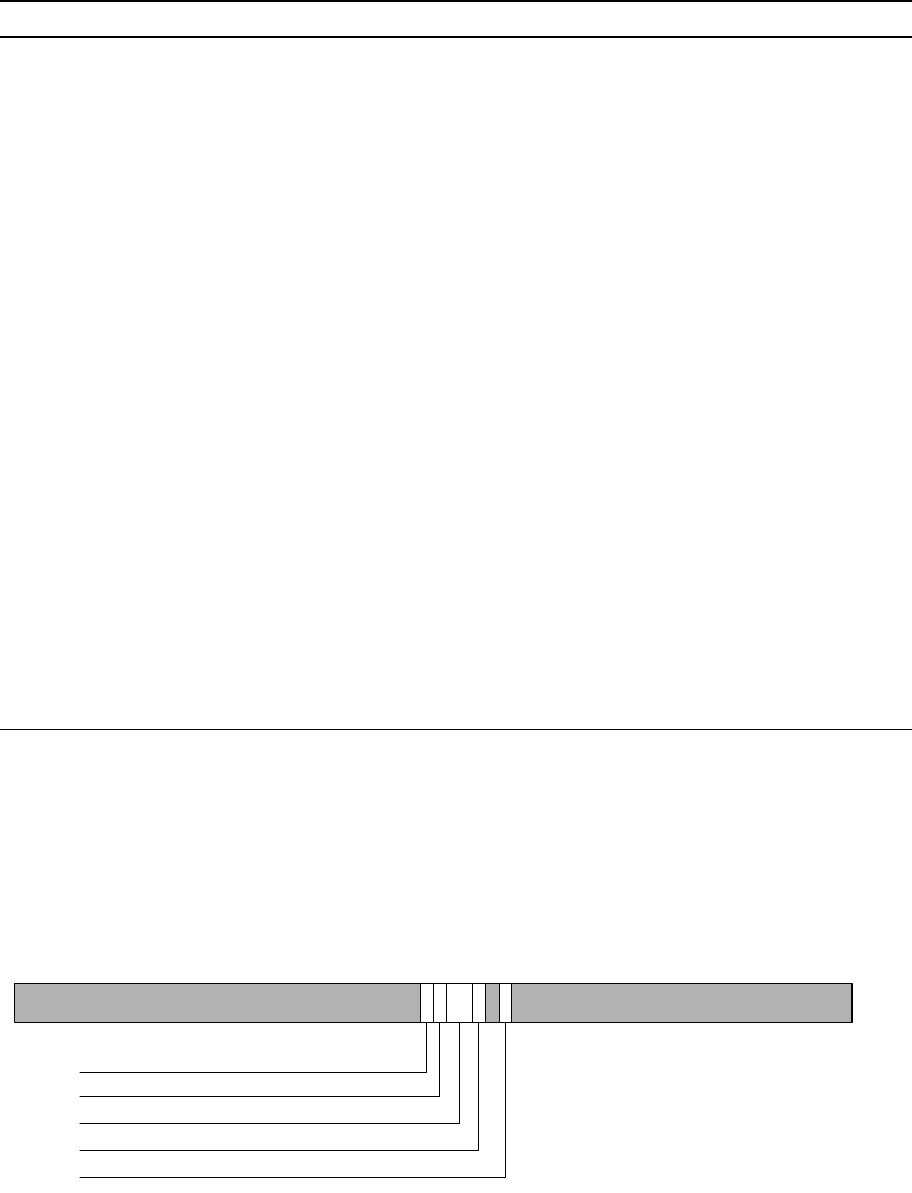

The hardware interrupt clear register (HW_INT_CLR) is a write-only register used to

clear edge-sensitive interrupt requests. See Section D.31 for more information about the

PALcode restriction concerning this register. Figure 5–19 shows the hardware interrupt

clear register.

Figure 5–19 Hardware Interrupt Clear Register

Table 5–7 Interrupt Summary Register Fields Description

Name Extent Type Description

Reserved [63:39] — —

EI[5:0] [38:33] RO External Interrupts

SL [32] RO Serial Line Interrupt

CR [31] RO Corrected Read Error Interrupts

PC[1:0] [30:29] RO Performance Counter Interrupts

PC0 when PC[0] is set.

PC1 when PC[1] is set.

SI[15:1] [28:14] RO Software Interrupts

Reserved [13:11] — —

ASTU, ASTS [10],[9] RO AST Interrupts

For each processor mode, the bit is set if an associated AST

interrupt is pending. This includes the mode’s ASTER and

ASTRR bits and whether the processor mode value held in the

IER_CM register is greater than or equal to the value for the

mode.

Reserved [8:5] — —

ASTE, ASTK [4],[3] RO AST Interrupts

For each processor mode, the bit is set if an associated AST

interrupt is pending. This includes the mode’s ASTER and

ASTRR bits and whether the processor mode value held in the

IER_CM register is greater than or equal to the value for the

mode.

Reserved [2:0] — —

63 29 2827 26 2533323130 0

SL

CR

PC[1:0]

MCHK_D

FBTP

LK

99

-

00

2

5

A