21264/EV68A Hardware Reference Manual

Initialization and Configuration 7–9

Energy Star Certification and Sleep Mode Flow

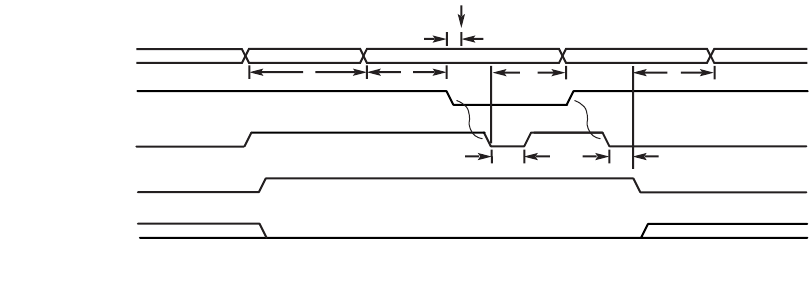

Figure 7–2 Fault Reset Sequence of Operation

7.3 Energy Star Certification and Sleep Mode Flow

The 21264/EV68A is Energy Star compliant. Energy Star is a program administered by

the Environmental Protection Agency to reduce energy consumption. For compliance,

a computer must automatically enter a low power sleep mode using 30 watts or less

after a specified period of inactivity. When the system is awakened, the user shall be

returned automatically to the same situation that existed prior to entering sleep mode.

During normal operation, the 21264/EV68A encounters inactive periods and enters a

mode that saves the entire active processor state to memory.

The PALcode is responsible for saving all necessary state to DRAM and flushing the

caches.

The sleep mode sequence of operations is triggered by the PALcode twice performing a

HW_MTPR to the Ibox SLEEP IPR. The first write prevents the assertion of

ClkFwdRst_H from fault-resetting the chip.

The PALcode then informs the system, in an implementation-dependent way, that it

may assert ClkFwdRst_H.

On the second HW_MTPR to the SLEEP IPR, the PLL begins to ramp down and the

21264/EV68A can then respond to the ClkFwdRst_H that was asserted by the system,

causing the outgoing clocks from the 21264/EV68A to stop.

The PLL ramp-down sequence takes exactly the same amount of time as the ramp up

sequence described in Section 7.1.3. The same internal duration counter is used and the

reset state machine transitions through the DOWN1, DOWN2, and DOWN3 states

which have similar PLL divisor ratios and clock speeds to the RAMP2, RAMP1, and

WAIT_NOMINAL states.

state

SromOE_L

ClkFwdRst_H

internal ClkFwdRst

RUN

WAIT_FAULT_RESET

internal clks aligned

external Clks

WAIT_ClkFwdRst0 WAIT_ClkFwdRst1

no min no min

b

c

A

e

f

g

a

FM-06488B.AI4

RUN