Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 104 SMSC LAN9311/LAN9311i

DATASHEET

1588_SEQ_ID_SRC_UUID_HI_TX_CAPTURE_1

00

1588_SRC_UUID_LO_TX_CAPTURE_1

00

1588_CLOCK_HI_RX_CAPTURE_2

00

1588_CLOCK_LO_RX_CAPTURE_2

00

1588_SEQ_ID_SRC_UUID_HI_RX_CAPTURE_2

00

1588_SRC_UUID_LO_RX_CAPTURE_2

00

1588_CLOCK_HI_TX_CAPTURE_2

00

1588_CLOCK_LO_TX_CAPTURE_2

00

1588_SEQ_ID_SRC_UUID_HI_TX_CAPTURE_2

00

1588_SRC_UUID_LO_TX_CAPTURE_2

00

1588_CLOCK_HI_RX_CAPTURE_MII

00

1588_CLOCK_LO_RX_CAPTURE_MII

00

1588_SEQ_ID_SRC_UUID_HI_RX_CAPTURE_MII

00

1588_SRC_UUID_LO_RX_CAPTURE_MII

00

1588_CLOCK_HI_TX_CAPTURE_MII

00

1588_CLOCK_LO_TX_CAPTURE_MII

00

1588_SEQ_ID_SRC_UUID_HI_TX_CAPTURE_MII

00

1588_SRC_UUID_LO_TX_CAPTURE_MII

00

1588_CLOCK_HI_CAPTURE_GPIO_8

00

1588_CLOCK_LO_CAPTURE_GPIO_8

00

1588_CLOCK_HI_CAPTURE_GPIO_9

00

1588_CLOCK_LO_CAPTURE_GPIO_9

00

1588_CLOCK_HI

45 1

1588_CLOCK_LO

45 1

1588_CLOCK_ADDEND

45 1

1588_CLOCK_TARGET_HI

45 1

1588_CLOCK_TARGET_LO

45 1

1588_CLOCK_TARGET_RELOAD_HI

45 1

1588_CLOCK_TARGET_RELOAD_LO

45 1

1588_AUX_MAC_HI

45 1

1588_AUX_MAC_LO

45 1

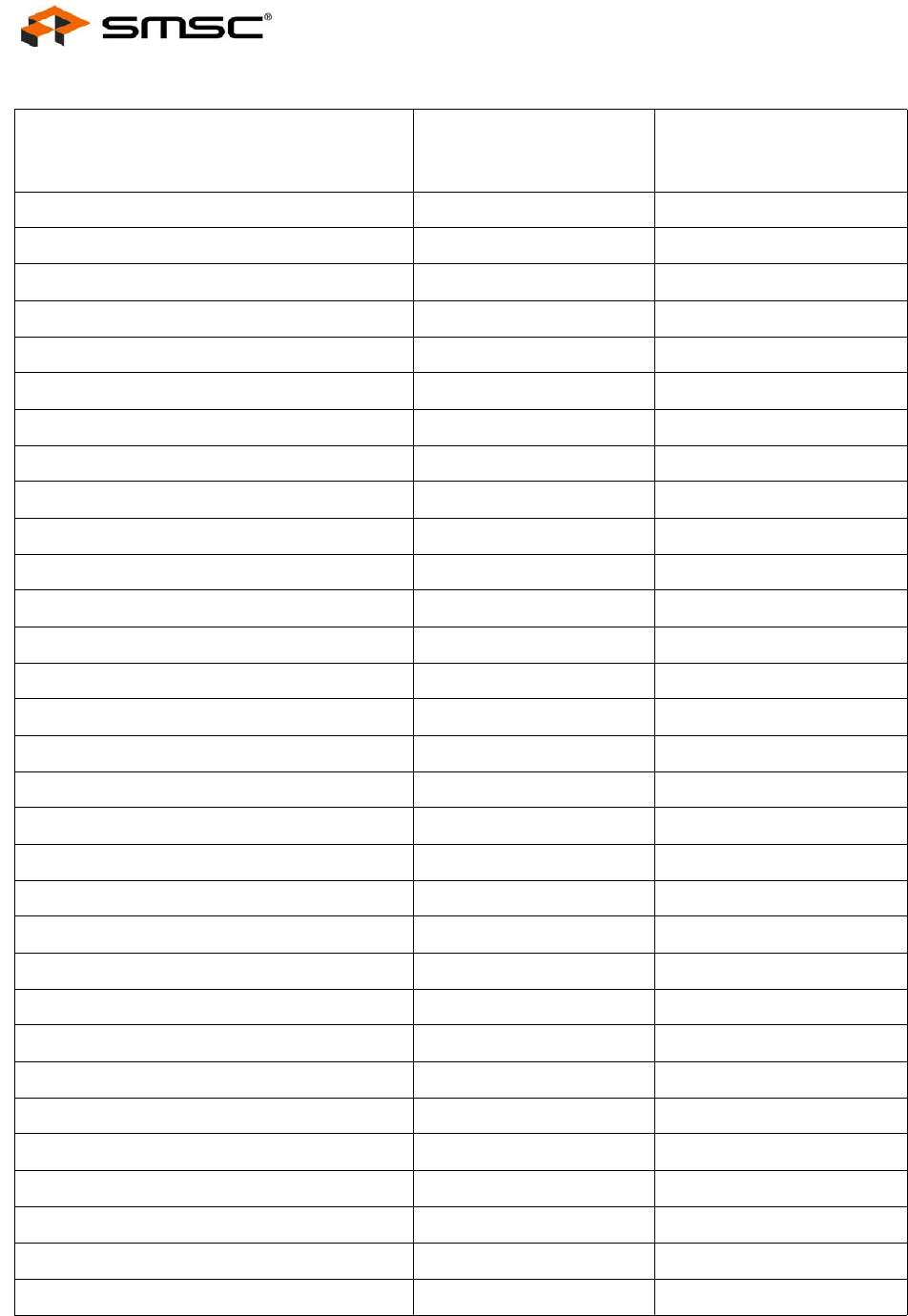

Table 8.1 Read After Write Timing Rules (continued)

REGISTER NAME

MINIMUM WAIT TIME FOR

READ FOLLOWING ANY

WRITE CYCLE (IN NS)

NUMBER OF BYTE_TEST

READS

(ASSUMING T

CYC

OF 45NS)