Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 93 Revision 1.4 (08-19-08)

DATASHEET

7.2.5.5 Half Vs. Full-Duplex

Half-duplex operation relies on the CSMA/CD (Carrier Sense Multiple Access / Collision Detect)

protocol to handle network traffic and collisions. In this mode, the carrier sense signal, CRS, responds

to both transmit and receive activity. If data is received while the PHY is transmitting, a collision results.

In full-duplex mode, the PHY is able to transmit and receive data simultaneously. In this mode, CRS

responds only to receive activity. The CSMA/CD protocol does not apply and collision detection is

disabled.

7.2.6 HP Auto-MDIX

HP Auto-MDIX facilitates the use of CAT-3 (10 BASE-T) or CAT-5 (100 BASE-T) media UTP

interconnect cable without consideration of interface wiring scheme. If a user plugs in either a direct

connect LAN cable or a cross-over patch cable, as shown in Figure 7.4 (See Note 7.1 on page 83), the

PHY is capable of configuring the TXPx/TXNx and RXPx/RXNx twisted pair pins for correct transceiver

operation.

The internal logic of the device detects the TX and RX pins of the connecting device. Since the RX

and TX line pairs are interchangeable, special PCB design considerations are needed to accommodate

the symmetrical magnetics and termination of an Auto-MDIX design.

The Auto-MDIX function can be disabled through bit 15 (AMDIXCTRL) of the Port x PHY Special

Control/Status Indication Register (PHY_SPECIAL_CONTROL_STAT_IND_x). When AMDIXCTRL is

cleared, Auto-MDIX can be selected via the auto_mdix_strap_x configuration strap. The MDIX can also

be configured manually via the manual_mdix_strap_x if both the AMDIXCTRL bit and the

auto_mdix_strap_x configuration strap are low. Refer to Section 3.2, "Pin Descriptions," on page 28 for

more information on the configuration straps.

When bit 15 (AMDIXCTRL) of the Port x PHY Special Control/Status Indication Register

(PHY_SPECIAL_CONTROL_STAT_IND_x) is set to 1, the Auto-MDIX capability is determined by bits

13 and 14 of the Port x PHY Special Control/Status Indication Register

(PHY_SPECIAL_CONTROL_STAT_IND_x).

7.2.7 MII MAC Interface

The MII MAC Interface is responsible for the transmission and reception of the Ethernet data to and

from the switch fabric MAC. The PHY is connected internally to the switch fabric MAC via standard

MII signals per IEEE 802.3.

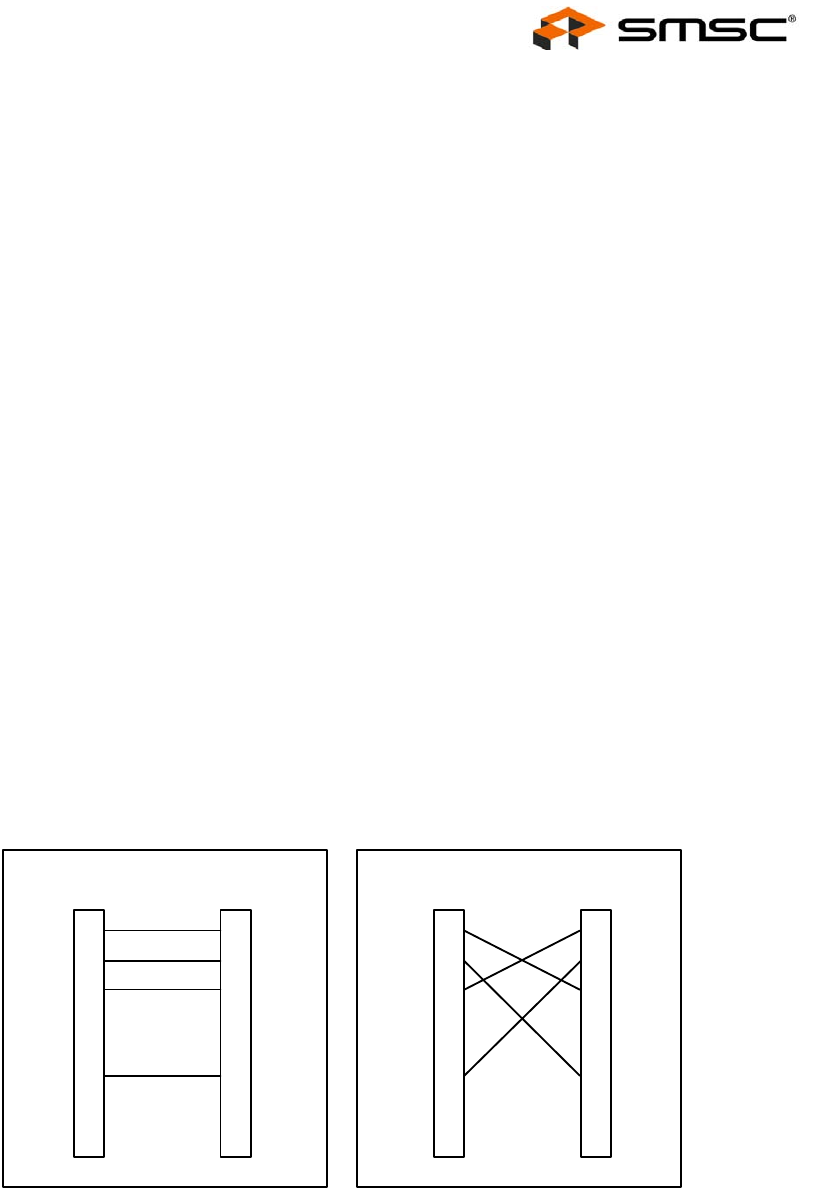

Figure 7.4 Direct Cable Connection vs. Cross-Over Cable Connection

1

2

3

4

5

6

7

8

TXPx

TXNx

RXPx

Not Used

Not Used

RXNx

Not Used

Not Used

1

2

3

4

5

6

7

8

TXPx

TXNx

RXPx

Not Used

Not Used

RXNx

Not Used

Not Used

Direct Connect Cable

RJ-45 8-pin straight-through

for 10BASE-T/100BASE-TX

signaling

1

2

3

4

5

6

7

8

TXPx

TXNx

RXPx

Not Used

Not Used

RXNx

Not Used

Not Used

1

2

3

4

5

6

7

8

TXPx

TXNx

RXPx

Not Used

Not Used

RXNx

Not Used

Not Used

Cross-Over Cable

RJ-45 8-pin cross-over for

10BASE-T/100BASE-TX

signaling