Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 302 SMSC LAN9311/LAN9311i

DATASHEET

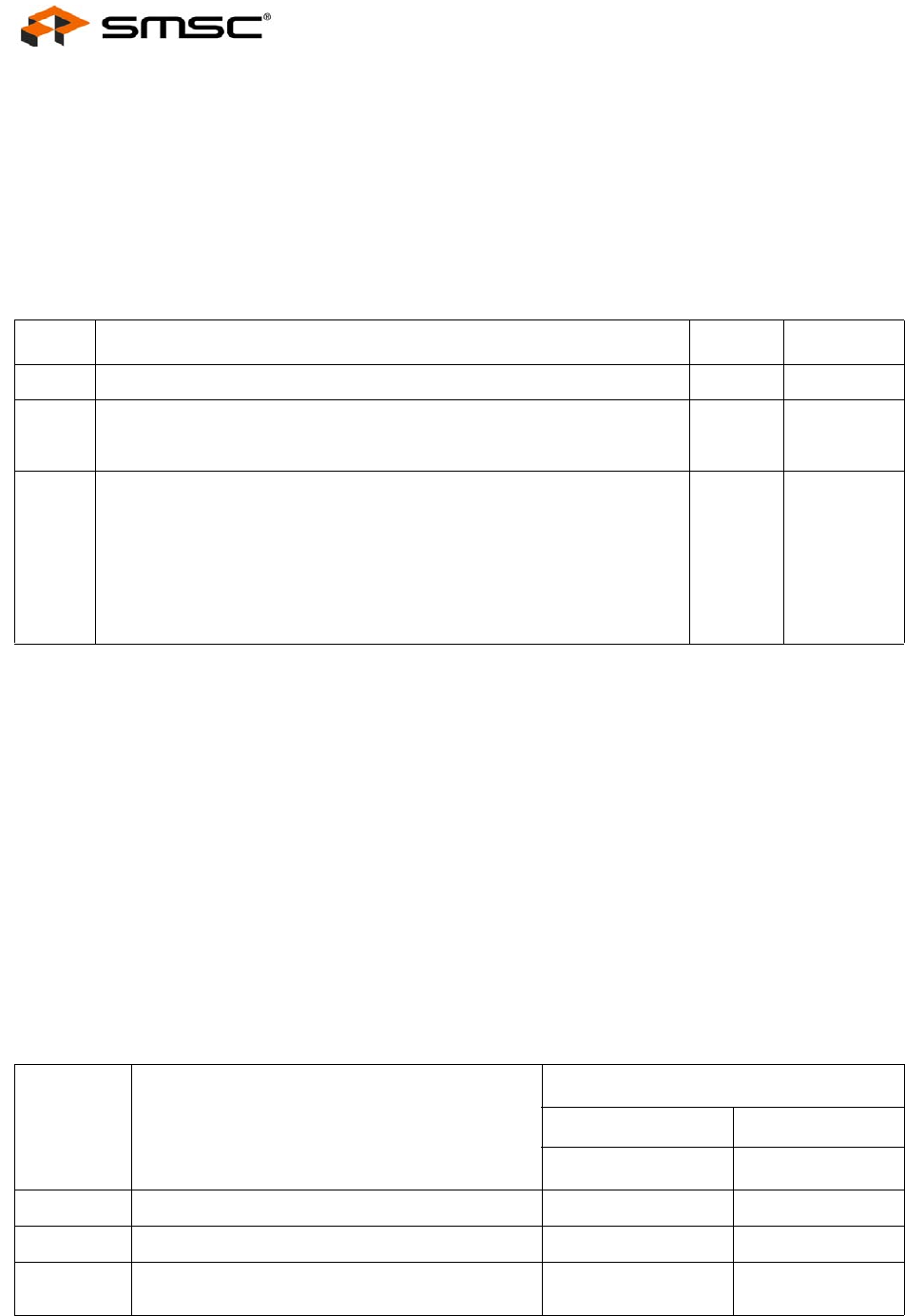

14.4.2.9 Port x PHY Special Modes Register (PHY_SPECIAL_MODES_x)

This read/write register is used to control the special modes of the Port x PHY.

Note: This register is re-written by the EEPROM Loader following the release of reset or a RELOAD

command. Refer to Section 10.2.4, "EEPROM Loader," on page 150 for more information.

Note 14.58 Register bits designated as NASR are reset when the Port x PHY Reset is generated via

the Reset Control Register (RESET_CTL). The NASR designation is only applicable when

the Reset (PHY_RST) bit of the Port x PHY Basic Control Register

(PHY_BASIC_CONTROL_x) is set.

Note 14.59 The default value of this field is determined by a combination of the configuration straps

autoneg_strap_x, speed_strap_x, and duplex_strap_x. If the autoneg_strap_x is 1, then

the default MODE[2:0] value is 111b. Else, the default value of this field is determined by

the remaining straps. MODE[2]=0, MODE[1]=(speed_strap_1 for Port 1 PHY,

speed_strap_2 for Port 2 PHY), and MODE[0]=(duplex_strap_1 for Port 1 PHY,

duplex_strap_2 for Port 2 PHY). Configuration strap values are latched upon the de-

assertion of a chip-level reset as described in Section 4.2.4, "Configuration Straps," on

page 40. Refer to Section 4.2.4, "Configuration Straps," on page 40 for configuration strap

definitions.

Note 14.60 The default value of this field is determined by the phy_addr_sel_strap configuration strap.

Refer to Section 7.1.1, "PHY Addressing," on page 82 for additional information.

Index (decimal): 18 Size: 16 bits

BITS DESCRIPTION TYPE DEFAULT

15:8 RESERVED RO -

7:5

PHY Mode (MODE[2:0])

This field controls the PHY mode of operation. Refer to Table 14.10 for a

definition of each mode.

R/W

NASR

Note 14.58

Note 14.59

4:0 PHY Address (PHYADD)

The PHY Address field determines the MMI address to which the PHY will

respond and is also used for initialization of the cipher (scrambler) key. Each

PHY must have a unique address. Refer to Section 7.1.1, "PHY

Addressing," on page 82 for additional information.

Note: No check is performed to ensure that this address is unique from

the other PHY addresses (Port 1 PHY, Port 2 PHY, and Virtual

PHY).

R/W

NASR

Note 14.58

Note 14.60

Table 14.10 MODE[2:0] Definitions

MODE[2:0] MODE DEFINITIONS

AFFECTED REGISTER BIT VALUES

PHY_BASIC_CONTROL_x PHY_AN_ADV_x

[13,12,10,8] [8,7,6,5]

000 10BASE-T Half Duplex. Auto-negotiation disabled. 0000 N/A

001 10BASE-T Full Duplex. Auto-negotiation disabled. 0001 N/A

010 100BASE-TX Half Duplex. Auto-negotiation

disabled. CRS is active during Transmit & Receive.

1000 N/A