Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 289 Revision 1.4 (08-19-08)

DATASHEET

14.4.2.1 Port x PHY Basic Control Register (PHY_BASIC_CONTROL_x)

This read/write register is used to configure the Port x PHY.

Note: This register is re-written in its entirety by the EEPROM Loader following the release of reset

or a RELOAD command. Refer to Section 10.2.4, "EEPROM Loader," on page 150 for

additional information.

Index (decimal): 0 Size: 16 bits

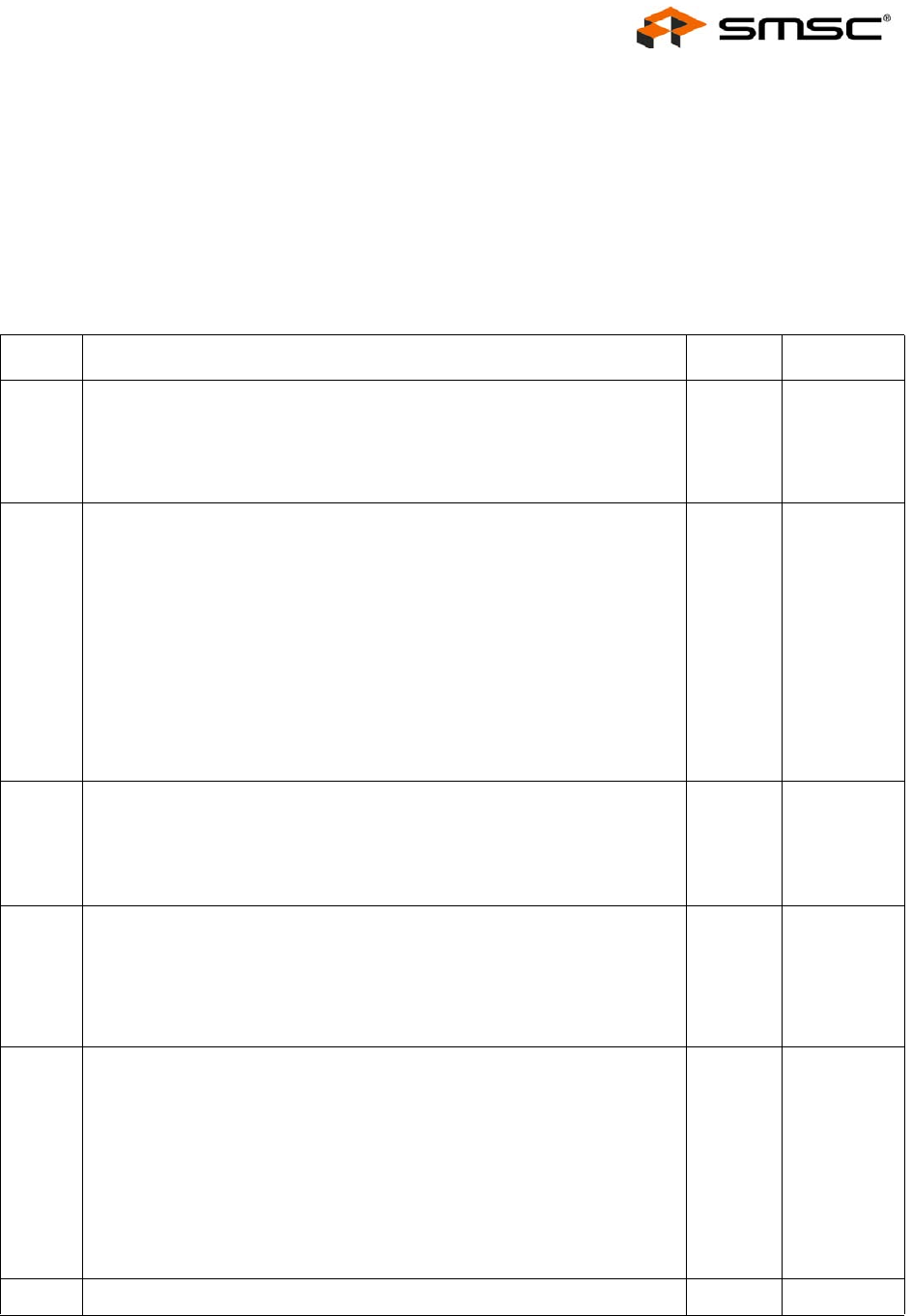

BITS DESCRIPTION TYPE DEFAULT

15 Reset (PHY_RST)

When set, this bit resets all the Port x PHY registers to their default state,

except those marked as NASR type. This bit is self clearing.

0: Normal operation

1: Reset

R/W

SC

0b

14

Loopback (PHY_LOOPBACK)

This bit enables/disables the loopback mode. When enabled, transmissions

from the switch fabric are not sent to network. Instead, they are looped back

into the switch fabric.

Note: If loopback is enabled during half-duplex operation, then the

Enable Receive Own Transmit bit in the Port x MAC Receive

Configuration Register (MAC_RX_CFG_x) must be set for the

specified port. Otherwise, the switch fabric will ignore receive

activity when transmitting in half-duplex mode.

0: Loopback mode disabled (normal operation)

1: Loopback mode enabled

R/W 0b

13

Speed Select LSB (PHY_SPEED_SEL_LSB)

This bit is used to set the speed of the Port x PHY when the Auto-

Negotiation (PHY_AN) bit is disabled.

0: 10 Mbps

1: 100 Mbps

R/W Note 14.49

12

Auto-Negotiation (PHY_AN)

This bit enables/disables Auto-Negotiation. When enabled, the Speed Select

LSB (PHY_SPEED_SEL_LSB) and Duplex Mode (PHY_DUPLEX) bits are

overridden.

0: Auto-Negotiation disabled

1: Auto-Negotiation enabled

R/W Note 14.50

11

Power Down (PHY_PWR_DWN)

This bit controls the power down mode of the Port x PHY. After this bit is

cleared the PHY may auto-negotiate with it’s partner station. This process

can take up to a few seconds to complete. Once Auto-Negotiation is

complete, bit 5 (Auto-Negotiation Complete) of the Port x PHY Basic Status

Register (PHY_BASIC_STATUS_x) will be set.

Note: The PHY_AN bit of this register must be cleared before setting this

bit.

0: Normal operation

1: General power down mode

R/W 0b

10

RESERVED RO -