Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 19 Revision 1.4 (08-19-08)

DATASHEET

1.3 Register Nomenclature

Table 1.2 describes the register bit attribute notation used throughout this document.

Many of these register bit notations can be combined. Some examples of this are shown below:

R/W: Can be written. Will return current setting on a read.

R/WAC: Will return current setting on a read. Writing anything clears the bit.

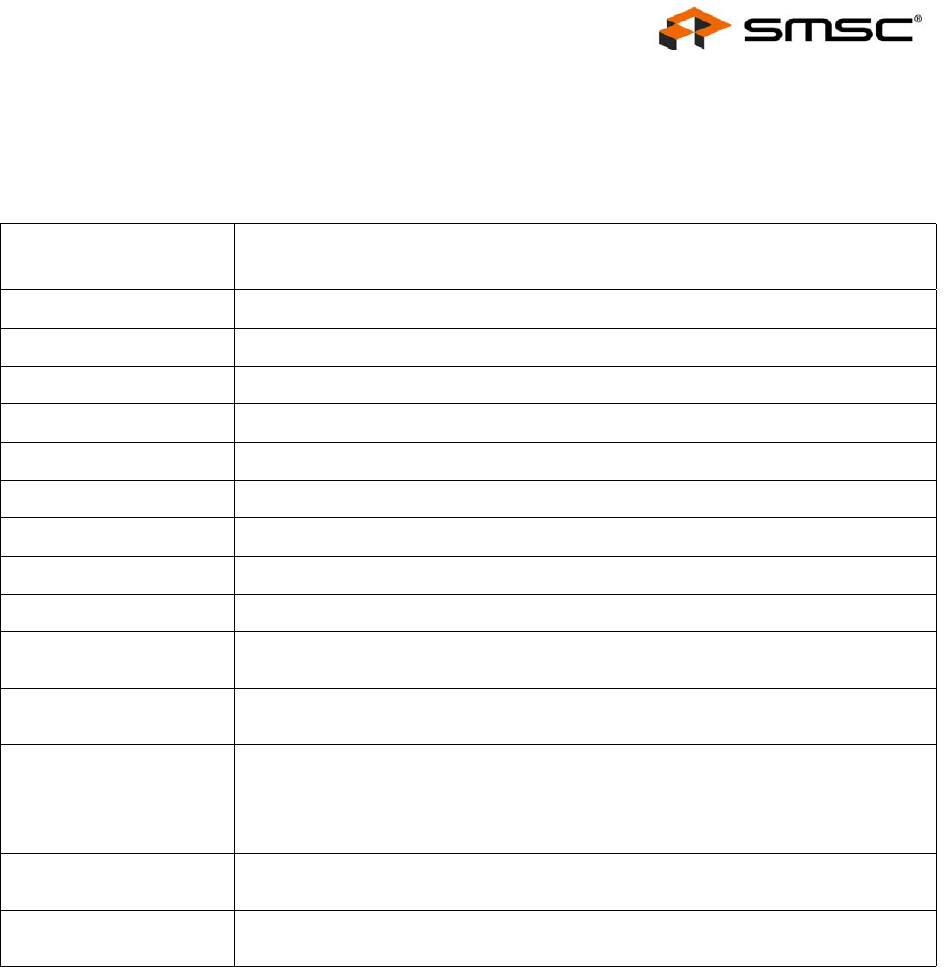

Table 1.2 Register Bit Types

REGISTER BIT TYPE

NOTATION REGISTER BIT DESCRIPTION

R Read: A register or bit with this attribute can be read.

W Read: A register or bit with this attribute can be written.

RO Read only: Read only. Writes have no effect.

WO Write only: If a register or bit is write-only, reads will return unspecified data.

WC Write One to Clear: writing a one clears the value. Writing a zero has no effect

WAC Write Anything to Clear: writing anything clears the value.

RC Read to Clear: Contents is cleared after the read. Writes have no effect.

LL Latch Low: Clear on read of register.

LH Latch High: Clear on read of register.

SC Self-Clearing: Contents are self-cleared after the being set. Writes of zero have no

effect. Contents can be read.

SS Self-Setting: Contents are self-setting after being cleared. Writes of one have no

effect. Contents can be read.

RO/LH Read Only, Latch High: Bits with this attribute will stay high until the bit is read. After

it is read, the bit will either remain high if the high condition remains, or will go low if

the high condition has been removed. If the bit has not been read, the bit will remain

high regardless of a change to the high condition. This mode is used in some Ethernet

PHY registers.

NASR Not Affected by Software Reset. The state of NASR bits do not change on assertion

of a software reset.

RESERVED Reserved Field: Reserved fields must be written with zeros to ensure future

compatibility. The value of reserved bits is not guaranteed on a read.