Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 381 Revision 1.4 (08-19-08)

DATASHEET

14.5.3.12 Switch Engine DIFFSERV Table Command Register (SWE_DIFFSERV_TBL_CFG)

This register is used to read and write the DIFFSERV table. A write to this address performs the

specified access. This table is used to map the received IP ToS/CS to a priority.

For a read access, the Operation Pending bit in the Switch Engine DIFFSERV Table Command Status

Register (SWE_DIFFSERV_TBL_CMD_STS) indicates when the command is finished. The Switch

Engine DIFFSERV Table Read Data Register (SWE_DIFFSERV_TBL_RD_DATA) can then be read.

For a write access, the Switch Engine DIFFSERV Table Write Data Register

(SWE_DIFFSERV_TBL_WR_DATA) register should be written first. The Operation Pending bit in the

Switch Engine DIFFSERV Table Command Status Register (SWE_DIFFSERV_TBL_CMD_STS)

indicates when the command is finished.

Register #: 1811h Size: 32 bits

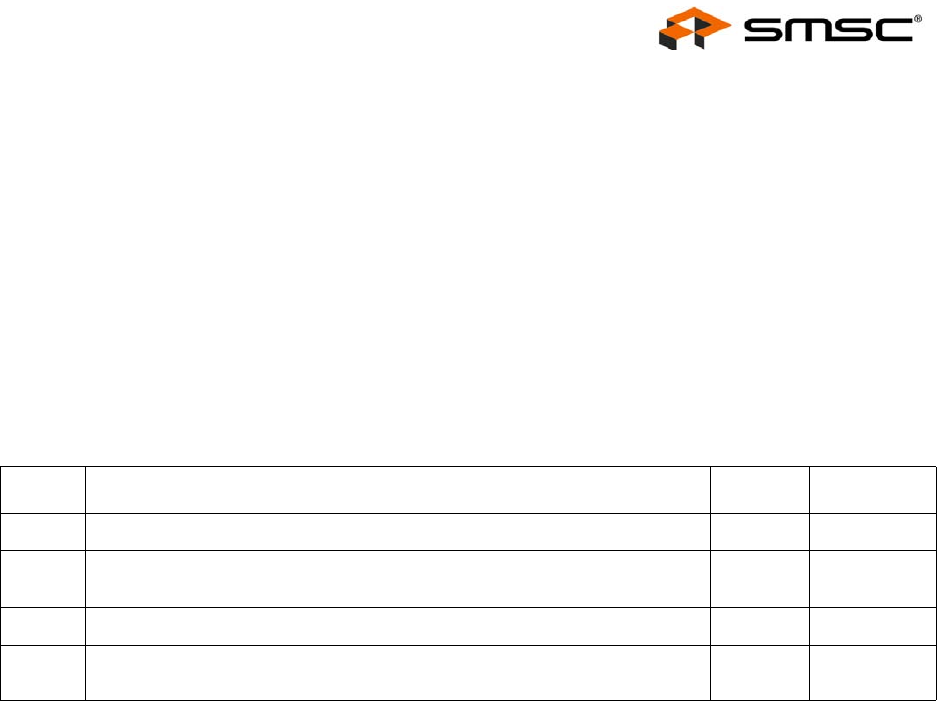

BITS DESCRIPTION TYPE DEFAULT

31:8 RESERVED RO -

7

DIFFSERV Table RnW

This bit specifies a read(1) or a write(0) command.

R/W 0b

6

RESERVED RO -

5:0

DIFFSERV Table Index

This field specifies the ToS/CS entry that is accessed.

R/W 0h