Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 84 SMSC LAN9311/LAN9311i

DATASHEET

7.2.1 100BASE-TX Transmit

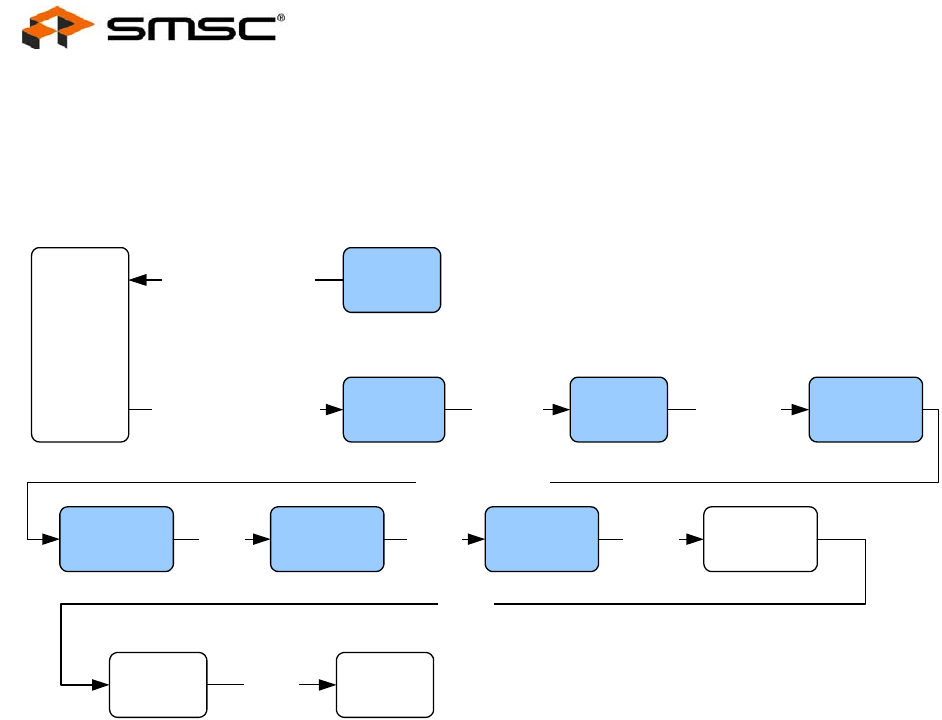

The 100BASE-TX transmit data path is shown in Figure 7.2. Shaded blocks are those which are

internal to the PHY. Each major block is explained in the following sections.

7.2.1.1 MII MAC Interface

For a transmission, the switch fabric MAC drives the transmit data to the PHYs MII MAC Interface.

The MII MAC Interface is described in detail in Section 7.2.7, "MII MAC Interface".

Note: The PHY is connected to the switch fabric MAC via standard MII signals. Refer to the IEEE

802.3 specification for additional details.

7.2.1.2 4B/5B Encoder

The transmit data passes from the MII block to the 4B/5B Encoder. This block encodes the data from

4-bit nibbles to 5-bit symbols (known as “code-groups”) according to Tab le 7.2. Each 4-bit data-nibble

is mapped to 16 of the 32 possible code-groups. The remaining 16 code-groups are either used for

control information or are not valid.

The first 16 code-groups are referred to by the hexadecimal values of their corresponding data nibbles,

0 through F. The remaining code-groups are given letter designations with slashes on either side. For

example, an IDLE code-group is /I/, a transmit error code-group is /H/, etc.

Figure 7.2 100BASE-TX Transmit Data Path

Port x

MAC

100M

TX Driver

MLT-3

Converter

NRZI

Converter

4B/5B

Encoder

Magnetics

CAT-5RJ45

100M

PLL

Internal

MII 25 MHz by 4 bits

Internal

MII Transmit Clock

25MHz by

5 bits

NRZI

MLT-3

MLT-3

MLT-3

MLT-3

Scrambler

and PISO

125 Mbps Serial

MII MAC

Interface

25MHz

by 4 bits