Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 124 SMSC LAN9311/LAN9311i

DATASHEET

The LAN9311/LAN9311i can be programmed to strip padding from the end of a transmit packet in the

event that the end of the packet does not align with the host burst boundary. This feature is necessary

when the LAN9311/LAN9311i is operating in a system that always performs multi-word bursts. In such

cases the LAN9311/LAN9311i must guarantee that it can accept data in multiples of the Burst length

regardless of the actual packet length. When configured to do so, the LAN9311/LAN9311i will accept

extra data at the end of the packet and will remove the extra padding before transmitting the packet.

The LAN9311/LAN9311i automatically removes data up to the boundary specified in the Buffer End

Alignment field specified in each TX command.

The host can instruct the LAN9311/LAN9311i to issue an interrupt when the buffer has been fully

loaded into the TX FIFO contained in the LAN9311/LAN9311i and transmitted. This feature is enabled

through the TX command ‘Interrupt on Completion’ field.

Upon completion of transmission, irrespective of success or failure, the status of the transmission is

written to the TX Status FIFO. TX status is available to the host and may be read using PIO operations.

An interrupt can be optionally enabled by the host to indicate the availability of a programmable

number TX status DWORDS.

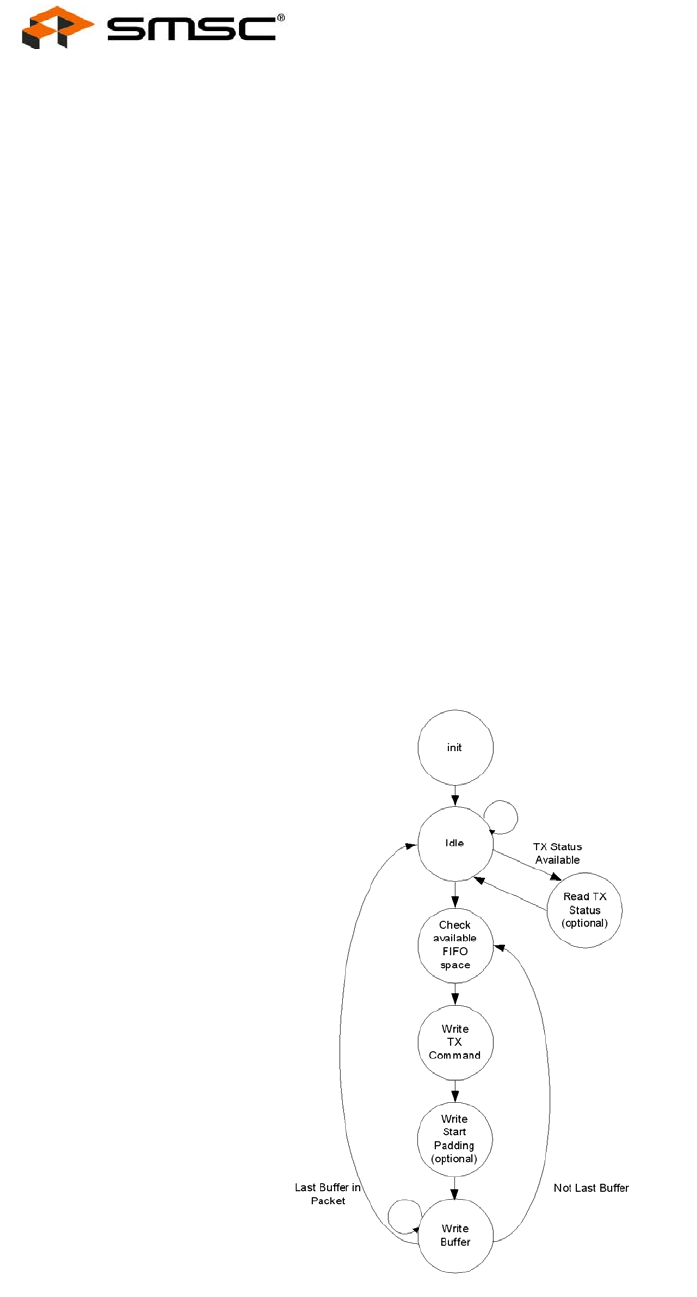

Before writing the TX command and payload data to the TX FIFO, the host must check the available

TX FIFO space by performing a PIO read of the TX FIFO Information Register (TX_FIFO_INF). The

host must ensure that it does not overfill the TX FIFO or the TX Error (TXE) flag will be asserted.

The host proceeds to write the TX command by first writing TX command ‘A’, then TX command ‘B’.

After writing the command, the host can then move the payload data into the TX FIFO. TX status

DWORDs are stored in the TX Status FIFO to be read by the host at a later time upon completion of

the data transmission onto the wire.

Figure 9.3 Simplified Host TX Flow Diagram