Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 135 Revision 1.4 (08-19-08)

DATASHEET

9.9.1.1 Receive Data FIFO Fast Forward

The RX data path implements an automatic data discard function. Using the RX Data FIFO Fast

Forward bit (RX_FFWD) in the Receive Datapath Control Register (RX_DP_CTRL), the host can

instruct the LAN9311/LAN9311i to skip the packet at the head of the RX Data FIFO. The RX Data FIFO

pointers are automatically incremented to the beginning of the next RX packet.

When performing a fast-forward, there must be at least 4 DWORDs of data in the RX Data FIFO for

the packet being discarded. For cases with less than 4 DWORDs, do not use RX_FFWD. In this case

data must be read from the RX Data FIFO and discarded using standard PIO read operations.

After initiating a fast-forward operation, do not perform any reads of the RX Data FIFO until the

RX_FFWD bit is cleared. Other resources can be accessed during this time (i.e., any registers and/or

the other three FIFO’s). Also note that the RX_FFWD will only fast-forward the RX Data FIFO, not the

RX Status FIFO. After an RX fast-forward operation the RX status must still be read from the RX Status

FIFO.

The receiver does not have to be stopped to perform a fast-forward operation.

9.9.1.2 Force Receiver Discard (Receiver Dump)

In addition to the Receive data Fast Forward feature, LAN9311/LAN9311i also implements a receiver

"dump" feature. This feature allows the host processor to flush the entire contents of the RX Data and

RX Status FIFOs. When activated, the read and write pointers for the RX Data and Status FIFO’s will

be returned to their reset state. To perform a receiver dump, the LAN9311/LAN9311i receiver must be

halted. Once the receiver stop completion is confirmed, the RX_DUMP bit can be set in the Receive

Configuration Register (RX_CFG). The RX_DUMP bit is cleared when the dump is complete. For more

information on stopping the receiver, please refer to Section 9.9.4, "Stopping and Starting the

Receiver". For more information on the RX_DUMP bit, please refer to Section 14.2.2.1, "Receive

Configuration Register (RX_CFG)," on page 181.

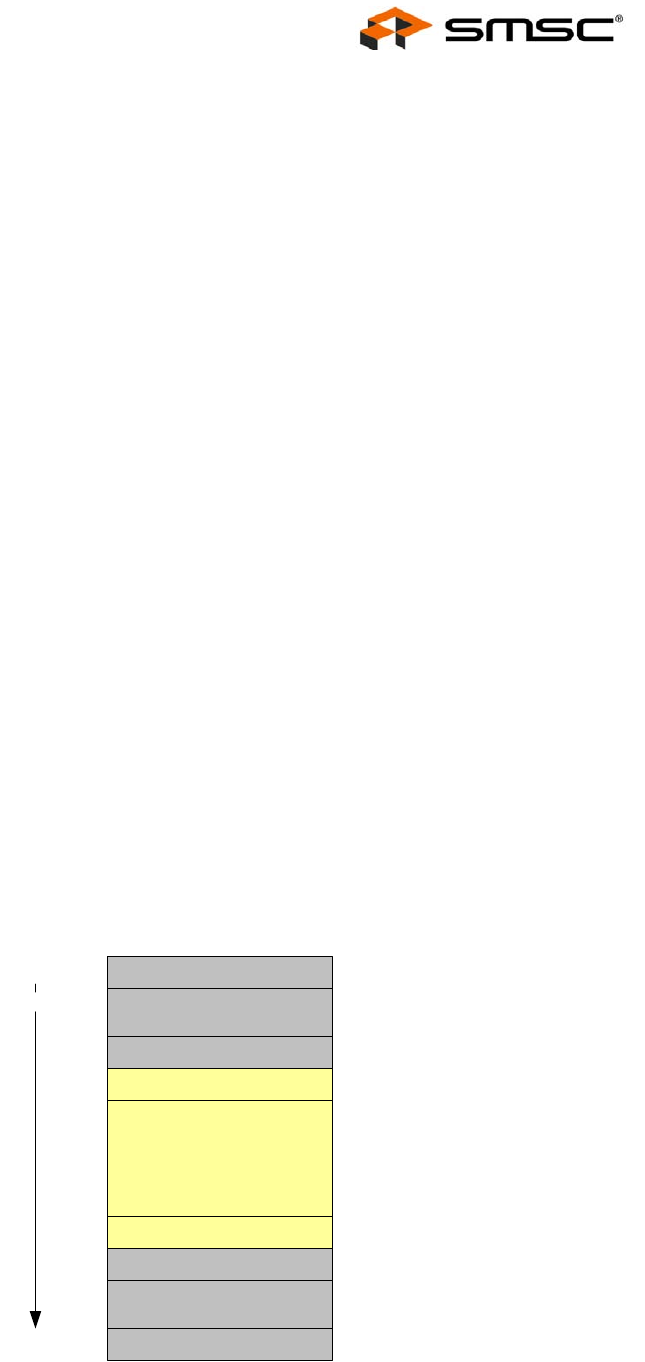

9.9.2 RX Packet Format

The RX status words can be read from the RX Status FIFO port, while the RX data packets can be

read from the RX Data FIFO. RX data packets are formatted in a specific manner before the host can

read them as shown in Figure 9.9. It is assumed that the host has previously read the associated

status word from the RX Status FIFO, to ascertain the data size and any error conditions.

Figure 9.9 RX Packet Format

ofs + First Data DWORD

.

.

.

.

Last Data DWORD

031

Host Read

Order

1st

2nd

Last

Optional Pad DWORD0

.

.

Optional Pad DWORDn

Optional offset DWORD0

.

.

Optional offset DWORDn