Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 170 SMSC LAN9311/LAN9311i

DATASHEET

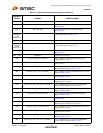

09Ch

FREE_RUN

Free Running Counter Register, Section 14.2.9.7

0A0h

RX_DROP

Host MAC RX Dropped Frames Counter Register,

Section 14.2.2.6

0A4h

MAC_CSR_CMD

Host MAC CSR Interface Command Register,

Section 14.2.2.7

0A4h

EEPROM

Loader

Access Only

PMI_DATA

PHY Management Interface Data Register (EEPROM

Loader Access Only), Section 14.2.7.1

0A8h

MAC_CSR_DATA

Host MAC CSR Interface Data Register, Section 14.2.2.8

0A8h

EEPROM

Loader

Access Only

PMI_ACCESS

PHY Management Interface Access Register (EEPROM

Loader Access Only), Section 14.2.7.2

0ACh

AFC_CFG

Host MAC Automatic Flow Control Configuration Register,

Section 14.2.2.9

0B0h - 0FCh

RESERVED

Reserved for Future Use

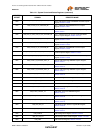

100h

1588_CLOCK_HI_RX_CAPTURE_1

Port 1 1588 Clock High-DWORD Receive Capture

Register, Section 14.2.5.1

104h

1588_CLOCK_LO_RX_CAPTURE_1

Port 1 1588 Clock Low-DWORD Receive Capture Register,

Section 14.2.5.2

108h

1588_SEQ_ID_SRC_UUID_HI_RX_CAPTURE_1

Port 1 1588 Sequence ID, Source UUID High-WORD

Receive Capture Register, Section 14.2.5.3

10Ch

1588_SRC_UUID_LO_RX_CAPTURE_1

Port 1 1588 Source UUID Low-DWORD Receive Capture

Register, Section 14.2.5.4

110h

1588_CLOCK_HI_TX_CAPTURE_1

Port 1 1588 Clock High-DWORD Transmit Capture

Register, Section 14.2.5.5

114h

1588_CLOCK_LO_TX_CAPTURE_1

Port 1 1588 Clock Low-DWORD Transmit Capture

Register, Section 14.2.5.6

118h

1588_SEQ_ID_SRC_UUID_HI_TX_CAPTURE_1

Port 1 1588 Sequence ID, Source UUID High-WORD

Transmit Capture Register, Section 14.2.5.7

11C

1588_SRC_UUID_LO_TX_CAPTURE_1

Port 1 1588 Source UUID Low-DWORD Transmit Capture

Register, Section 14.2.5.8

120h

1588_CLOCK_HI_RX_CAPTURE_2

Port 2 1588 Clock High-DWORD Receive Capture

Register, Section 14.2.5.1

124h

1588_CLOCK_LO_RX_CAPTURE_2

Port 2 1588 Clock Low-DWORD Receive Capture Register,

Section 14.2.5.2

128h

1588_SEQ_ID_SRC_UUID_HI_RX_CAPTURE_2

Port 2 1588 Sequence ID, Source UUID High-WORD

Receive Capture Register, Section 14.2.5.3

12Ch

1588_SRC_UUID_LO_RX_CAPTURE_2

Port 2 1588 Source UUID Low-DWORD Receive Capture

Register, Section 14.2.5.4

130h

1588_CLOCK_HI_TX_CAPTURE_2

Port 2 1588 Clock High-DWORD Transmit Capture

Register, Section 14.2.5.5

134h

1588_CLOCK_LO_TX_CAPTURE_2

Port 2 1588 Clock Low-DWORD Transmit Capture

Register, Section 14.2.5.6

138h

1588_SEQ_ID_SRC_UUID_HI_TX_CAPTURE_2

Port 2 1588 Sequence ID, Source UUID High-WORD

Transmit Capture Register, Section 14.2.5.7

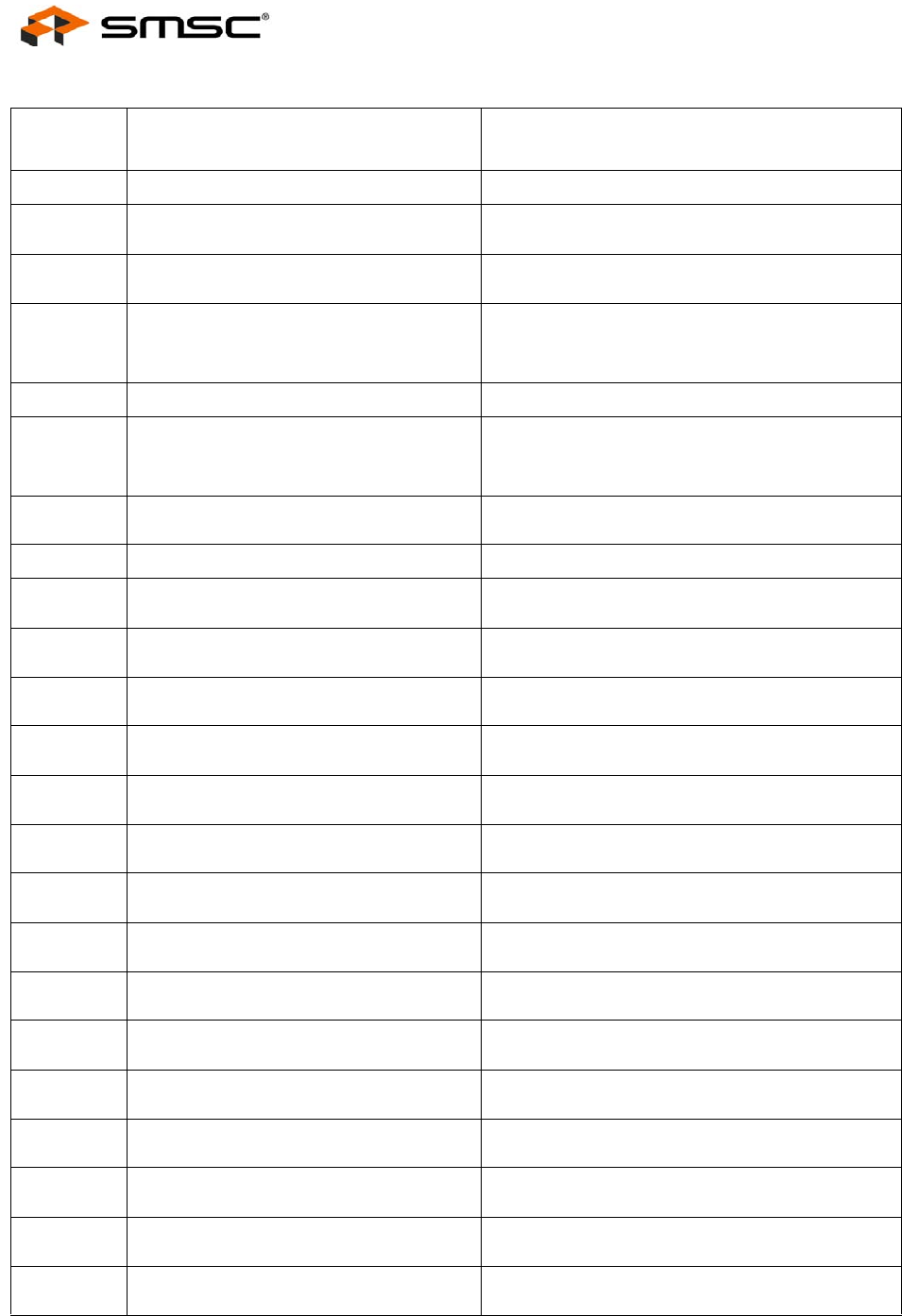

Table 14.1 System Control and Status Registers (continued)

ADDRESS

OFFSET SYMBOL REGISTER NAME