Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 397 Revision 1.4 (08-19-08)

DATASHEET

14.5.3.26.1 INGRESS RATE TABLE REGISTERS

The ingress rate metering/color table consists of 24 Committed Information Rate (CIR) registers (one

per port/priority), a Committed Burst Size register, and an Excess Burst Size register. All metering/color

table registers are 16-bits in size and are accessed indirectly via the Switch Engine Ingress Rate

Command Register (SWE_INGRSS_RATE_CMD). Descriptions of these registers are detailed in

Table 14.13 below.

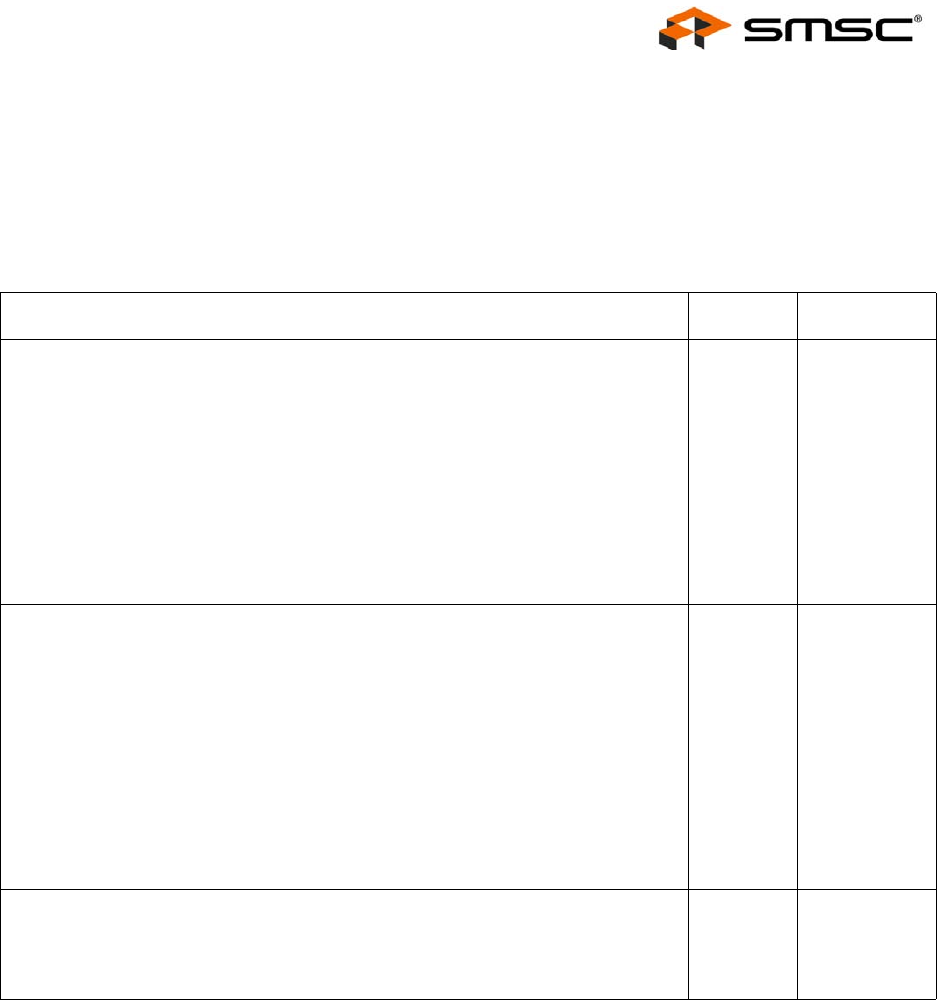

Table 14.13 Metering/Color Table Register Descriptions

DESCRIPTION TYPE DEFAULT

Excess Burst Size

This register specifies the maximum excess burst size in bytes. Bursts larger than

this value that exceed the excess data rate are dropped.

Note: Either this value or the Committed Burst Size should be set larger than or

equal to the largest possible packet expected.

Note: All of the Excess Burst token buckets are initialized to this default value.

If a lower value is programmed into this register, the token buckets will

need to be normally depleted below this value before this value has any

affect on limiting the token bucket maximum values.

This register is 16-bits wide.

R/W 0600h

Committed Burst Size

This register specifies the maximum committed burst size in bytes. Bursts larger

than this value that exceed the committed data rate are subjected to random

dropping.

Note: Either this value or the Excess Burst Size should be set larger than or

equal to the largest possible packet expected.

Note: All of the Committed Burst token buckets are initialized to this default

value. If a lower value is programmed into this register, the token buckets

will need to be normally depleted below this value before this value has

any affect on limiting the token bucket maximum values.

This register is 16-bits wide.

R/W 0600h

Committed Information Rate (CIR)

These registers specify the committed data rate for the port/priority pair. The rate

is specified in time per byte. The time is this value plus 1 times 20nS.

There are 24 of these registers each 16-bits wide.

R/W 0014h