Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 265 Revision 1.4 (08-19-08)

DATASHEET

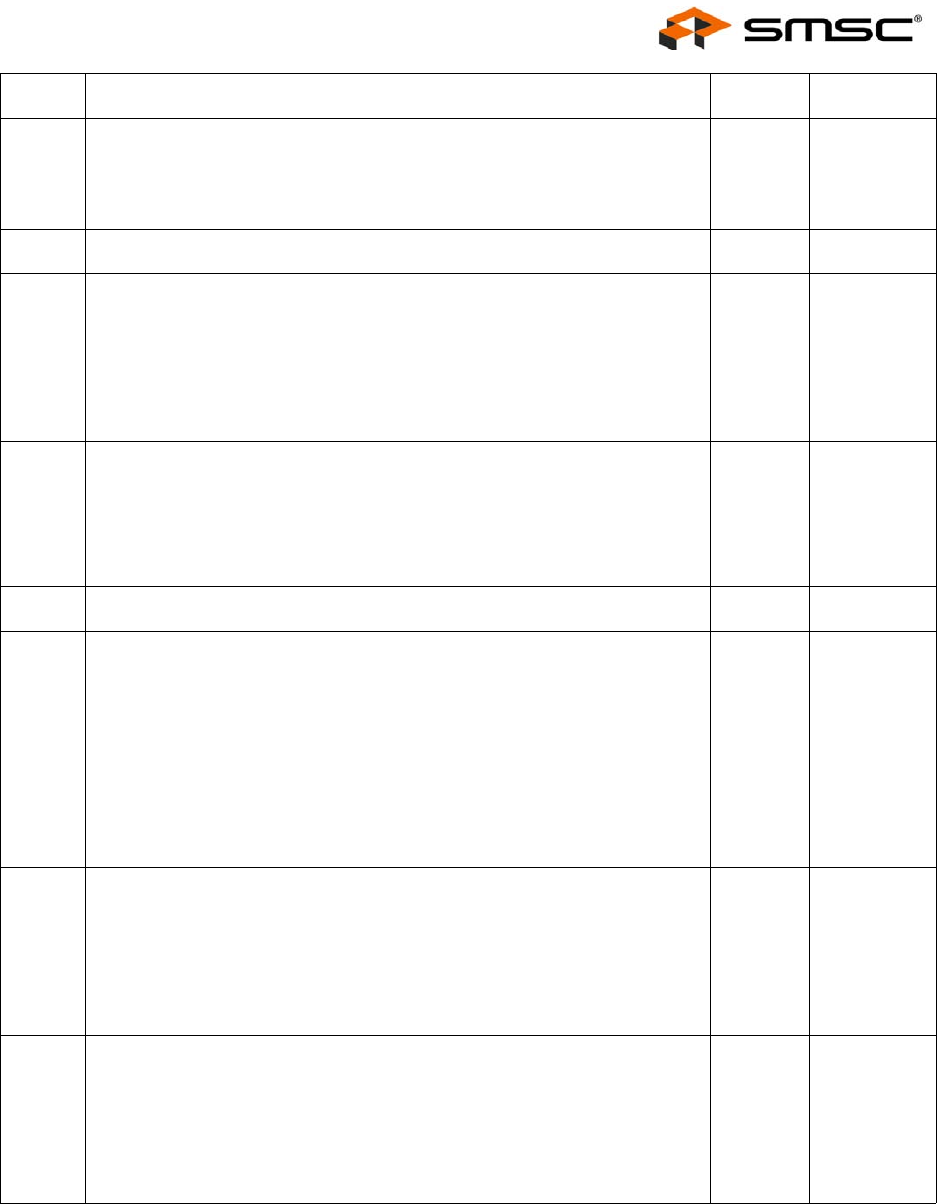

9 Wake-On-LAN Enable (WOL_EN)

When set, the PME signal (if enabled via the PME_EN bit) will be asserted

in accordance with the PME_IND bit upon a WOL event. When set, the

PME_INT bit in the Interrupt Status Register (INT_STS) will also be asserted

upon a WOL event, regardless of the setting of the PME_EN bit.

R/W 0b

8:7

RESERVED RO -

6 PME Buffer Type (PME_TYPE)

When this bit is cleared, the PME pin functions as an open-drain buffer for

use in a wired-or configuration. When set, the PME pin is a push-pull driver.

Note: When PME is configured as an open-drain output, the PME_POL

field of this register is ignored and the output is always active low.

0: PME pin open-drain output

1: PME pin push-pull driver

R/W

NASR

0b

5

Wake On LAN Status (WOL_STS)

This bit indicates that a wake-up frame or magic packet was detected by the

Host MAC.

In order to clear this bit, it is required that the event in the Host MAC be

cleared as well. The event sources are described in Section 4.3, "Power

Management," on page 46.

R/WC 0b

4

RESERVED RO -

3 PME Indication (PME_IND)

The PME signal can be configured as a pulsed output or a static signal,

which is asserted upon detection of a wake-up event. When set, the PME

signal will pulse active for 50mS upon detection of a wake-up event. When

cleared, the PME signal is driven continuously upon detection of a wake-up

event.

0: PME 50mS pulse on detection of event

1: PME driven continuously on detection of event

The PME signal can be deactivated by clearing the WOL_STS bit or by

clearing the appropriate enable.

R/W 0b

2

PME Polarity (PME_POL)

This bit controls the polarity of the PME signal. When set, the PME output

is an active high signal. When cleared, it is active low.

Note: When PME is configured as an open-drain output, this field is

ignored and the output is always active low.

0: PME active low

1: PME active high

R/W

NASR

0b

1

PME Enable (PME_EN)

When set, this bit enables the external PME signal pin. When cleared, the

external PME signal is disabled.

Note: This bit does not affect the PME_INT interrupt bit of the Interrupt

Status Register (INT_STS).

0: PME pin disabled

1: PME pin enabled

R/W 0b

BITS DESCRIPTION TYPE DEFAULT