Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 181 Revision 1.4 (08-19-08)

DATASHEET

14.2.2 Host MAC & FIFO’s

This section details the Host MAC and TX/RX FIFO related System CSR’s.

These Host Bus Interface accessible registers allow for the configuration of the TX/RX FIFO’s, Host

MAC and indirect access to the complete set of Host MAC CSR’s. The Host MAC CSR’s are

accessible through the Host Bus Interface via the Host MAC CSR Interface Command Register

(MAC_CSR_CMD) and Host MAC CSR Interface Data Register (MAC_CSR_DATA).

Note: For more information on the TX/RX FIFO’s, refer to Section 14.1, "TX/RX FIFO Ports".

Note: The full list of Host MAC CSR’s are described in Section 14.3, "Host MAC Control and Status

Registers," on page 271. For more information on the Host MAC, refer to Chapter 9, "Host

MAC," on page 113.

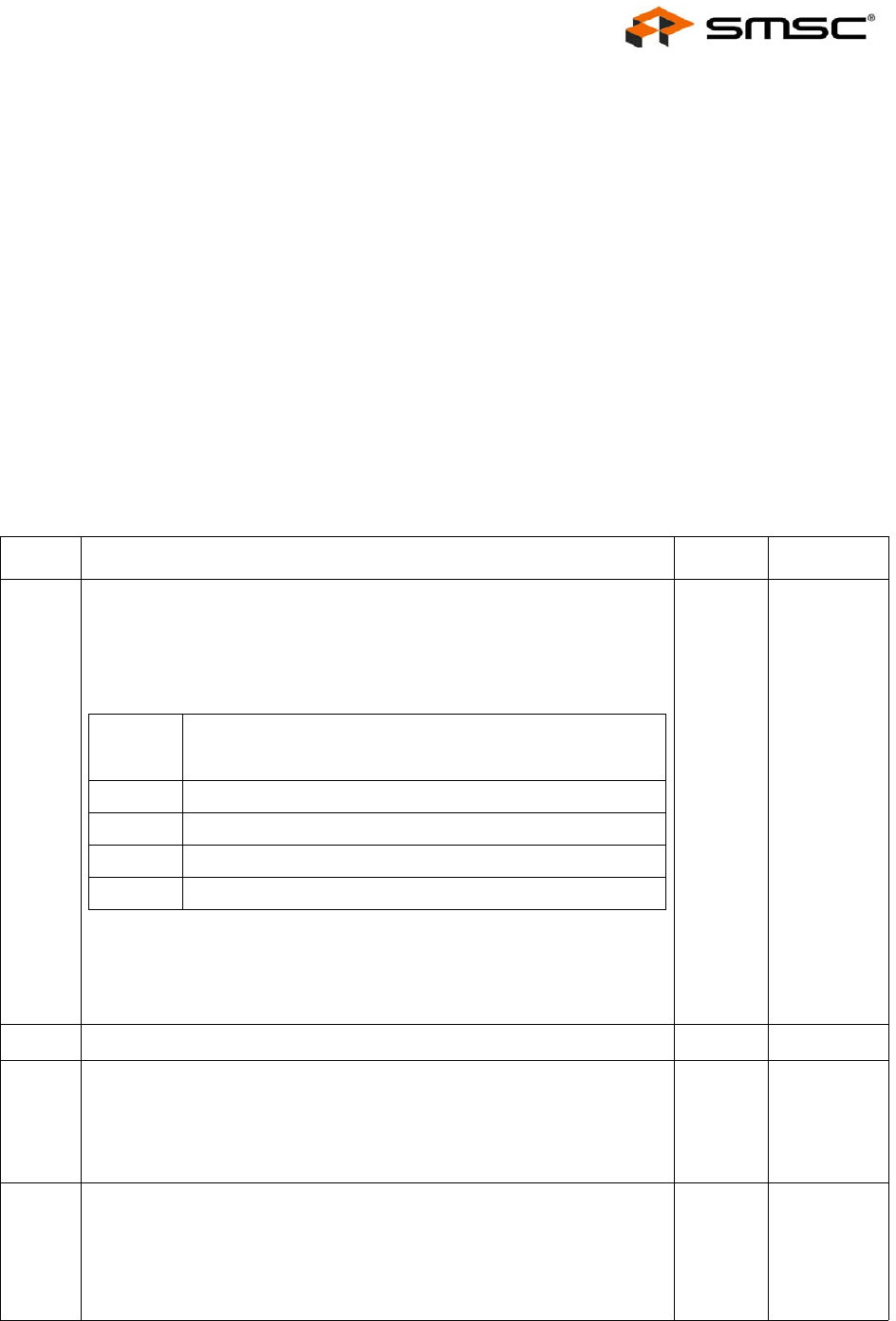

14.2.2.1 Receive Configuration Register (RX_CFG)

This register controls the Host MAC receive engine.

Offset: 06Ch Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:30 RX End Alignment (RX_EA)

This field specifies the alignment that must be maintained on the last data

transfer of a buffer. The LAN9311/LAN9311i will add extra DWORD’s of

data up to the alignment specified in the table below. The host is

responsible for removing these extra DWORD’s. This mechanism can be

used to maintain cache line alignment on host processors.

Note: The desired RX End Alignment must be set before reading a

packet. The RX End Alignment can be changed between reading

receive packets, but must not be changed if the packet is partially

read.

R/W 00b

29:28

RESERVED RO -

27:16

RX DMA Count (RX_DMA_CNT)

This 12-bit field indicates the amount of data, in DWORD’s, to be

transferred out of the RX Data FIFO before asserting the RX DMA Interrupt

(RXD_INT). After being set, this field is decremented for each DWORD of

data that is read from the RX Data FIFO. This field can be overwritten with

a new value before it reaches zero.

R/W 000h

15

Force RX Discard (RX_DUMP)

When a 1 is written to this bit, the RX Data and Status FIFO’s are cleared

of all pending data and the RX data and status pointers are cleared to zero.

Note: Please refer to Section 9.9.1.2, "Force Receiver Discard (Receiver

Dump)," on page 135 for a detailed description regarding the use

of RX_DUMP.

WO

SC

0b

BIT

VALUES

[31:30] END ALIGNMENT

00 4-Byte Alignment

01 16-Byte Alignment

10 32-Byte Alignment

11 RESERVED