Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 311 Revision 1.4 (08-19-08)

DATASHEET

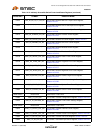

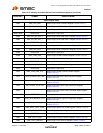

0455h

MAC_TX_65_TO_127_CNT_MII

Port 0 MAC Transmit 65 to 127 Byte Count Register,

Section 14.5.2.29

0456h

MAC_TX_128_TO_255_CNT_MII

Port 0 MAC Transmit 128 to 255 Byte Count Register,

Section 14.5.2.30

0457h

MAC_TX_256_TO_511_CNT_MII

Port 0 MAC Transmit 256 to 511 Byte Count Register,

Section 14.5.2.31

0458h

MAC_TX_512_TO_1023_CNT_MII

Port 0 MAC Transmit 512 to 1023 Byte Count Register,

Section 14.5.2.32

0459h

MAC_TX_1024_TO_MAX_CNT_MII

Port 0 MAC Transmit 1024 to Max Byte Count Register,

Section 14.5.2.33

045Ah

MAC_TX_UNDSZE_CNT_MII

Port 0 MAC Transmit Undersize Count Register,

Section 14.5.2.34

045Bh RESERVED Reserved for Future Use

045Ch

MAC_TX_PKTLEN_CNT_MII

Port 0 MAC Transmit Packet Length Count Register,

Section 14.5.2.35

045Dh

MAC_TX_BRDCST_CNT_MII

Port 0 MAC Transmit Broadcast Count Register,

Section 14.5.2.36

045Eh

MAC_TX_MULCST_CNT_MII

Port 0 MAC Transmit Multicast Count Register,

Section 14.5.2.37

045Fh MAC_TX_LATECOL_MII Port 0 MAC Transmit Late Collision Count Register,

Section 14.5.2.38

0460h MAC_TX_EXCOL_CNT_MII Port 0 MAC Transmit Excessive Collision Count Register,

Section 14.5.2.39

0461h

MAC_TX_SNGLECOL_CNT_MII

Port 0 MAC Transmit Single Collision Count Register,

Section 14.5.2.40

0462h

MAC_TX_MULTICOL_CNT_MII

Port 0 MAC Transmit Multiple Collision Count Register,

Section 14.5.2.41

0463h

MAC_TX_TOTALCOL_CNT_MII

Port 0 MAC Transmit Total Collision Count Register,

Section 14.5.2.42

0464-047Fh RESERVED Reserved for Future Use

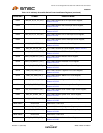

0480h MAC_IMR_MII Port 0 MAC Interrupt Mask Register, Section 14.5.2.43

0481h MAC_IPR_MII Port 0 MAC Interrupt Pending Register, Section 14.5.2.44

0482h-07FFh RESERVED Reserved for Future Use

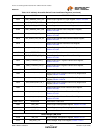

Switch Port 1 CSRs

0800h MAC_VER_ID_1 Port 1 MAC Version ID Register, Section 14.5.2.1

0801h MAC_RX_CFG_1 Port 1 MAC Receive Configuration Register, Section 14.5.2.2

0802h-080Fh RESERVED Reserved for Future Use

0810h MAC_RX_UNDSZE_CNT_1 Port 1 MAC Receive Undersize Count Register,

Section 14.5.2.3

0811h MAC_RX_64_CNT_1 Port 1 MAC Receive 64 Byte Count Register, Section 14.5.2.4

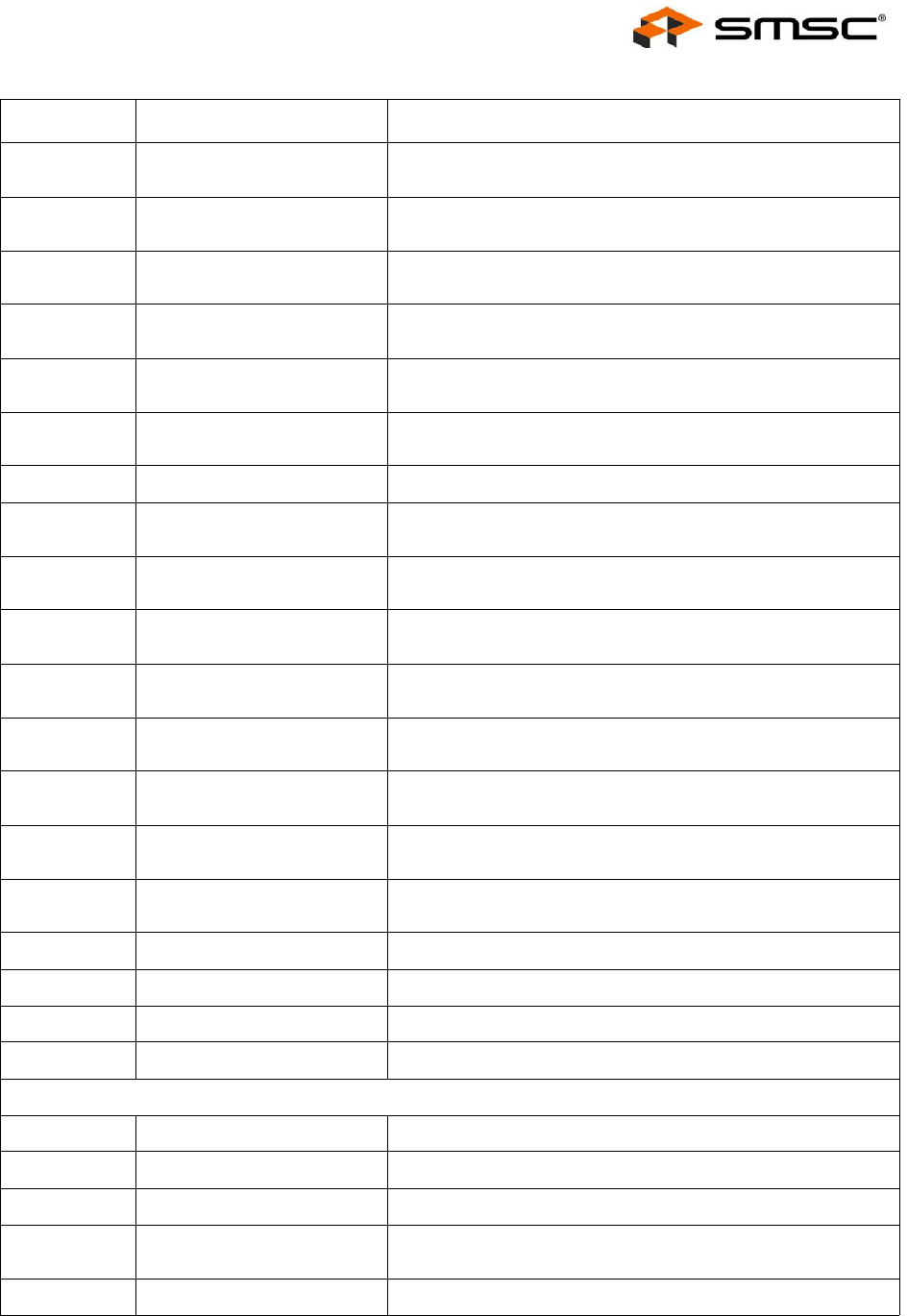

Table 14.12 Indirectly Accessible Switch Control and Status Registers (continued)

REGISTER # SYMBOL REGISTER NAME