Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 227 Revision 1.4 (08-19-08)

DATASHEET

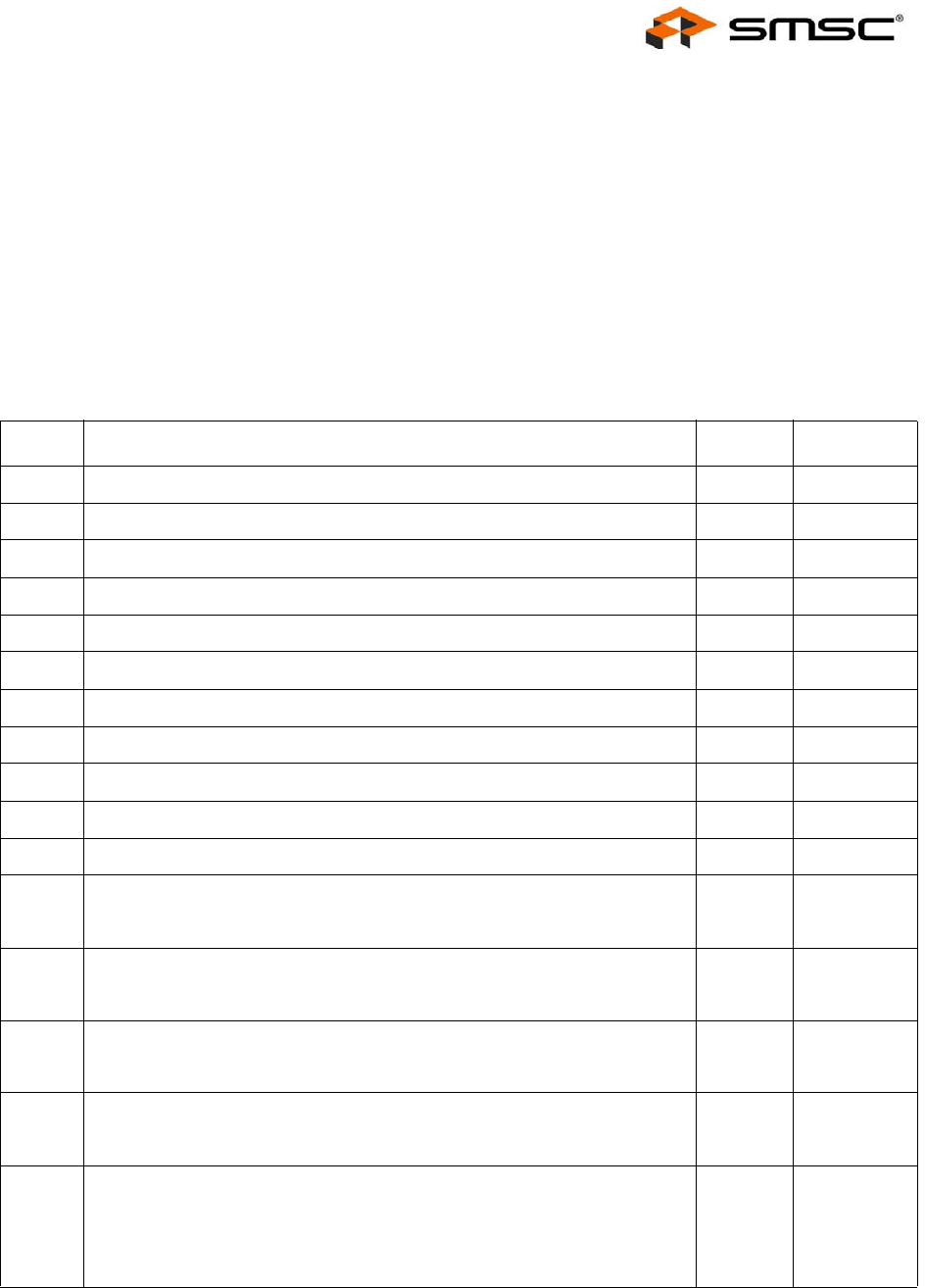

14.2.5.23 1588 Interrupt Status and Enable Register (1588_INT_STS_EN)

This read/write register contains the IEEE 1588 interrupt status and enable bits.

Writing a 1 to any of the interrupt status bits acknowledges and clears the interrupt. If enabled, these

interrupt bits are cascaded into bit 29 (1588_EVNT) of the Interrupt Status Register (INT_STS). Writing

a 1 to any of the interrupt enable bits will enable the corresponding interrupt as a source. Status bits

will still reflect the status of the interrupt source regardless of whether the source is enabled as an

interrupt in this register. Bit 29 (1588_EVNT_EN) of the Interrupt Enable Register (INT_EN) must also

be set in order for an actual system level interrupt to occur. Refer to Chapter 5, "System Interrupts,"

on page 49 for additional information.

Offset: 198h Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:25 RESERVED RO -

24

1588 Port 2 RX Interrupt Enable (1588_PORT2_RX_EN) R/W 0b

23

1588 Port 2 TX Interrupt Enable (1588_PORT2_TX_EN) R/W 0b

22

1588 Port 1 RX Interrupt Enable (1588_PORT1_RX_EN) R/W 0b

21

1588 Port 1 TX Interrupt Enable (1588_PORT1_TX_EN) R/W 0b

20

1588 Port 0(Host MAC) RX Interrupt Enable (1588_MII_RX_EN) R/W 0b

19

1588 Port 0(Host MAC) TX Interrupt Enable (1588_MII_TX_EN) R/W 0b

18

GPIO9 1588 Interrupt Enable (1588_GPIO9_EN) R/W 0b

17

GPIO8 1588 Interrupt Enable (1588_GPIO8_EN) R/W 0b

16

1588 Timer Interrupt Enable (1588_TIMER_EN) R/W 0b

15:9

RESERVED RO -

8

1588 Port 2 RX Interrupt (1588_PORT2_RX_INT)

This interrupt indicates that a packet received by Port 2 matches the

configured PTP packet and the 1588 clock was captured.

R/WC 0b

7

1588 Port 2 TX Interrupt (1588_PORT2_TX_INT)

This interrupt indicates that a packet transmitted by Port 2 matches the

configured PTP packet and the 1588 clock was captured.

R/WC 0b

6

1588 Port 1 RX Interrupt (1588_PORT1_RX_INT)

This interrupt indicates that a packet received by Port 1 matches the

configured PTP packet and the 1588 clock was captured.

R/WC 0b

5

1588 Port 1 TX Interrupt (1588_PORT1_TX_INT)

This interrupt indicates that a packet transmitted by Port 1 matches the

configured PTP packet and the 1588 clock was captured.

R/WC 0b

4

1588 Port 0(Host MAC) RX Interrupt (1588_MII_RX_INT)

This interrupt indicates that a packet from the switch fabric to the Host MAC

the matches the configured PTP packet and the 1588 clock was captured.

Note: For Port 0, receive is defined as data from the switch fabric, while

transmit is

to the switch fabric.

R/WC 0b