Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 47 Revision 1.4 (08-19-08)

DATASHEET

4.3.1 Port 1 & 2 PHY Power Management

The Port 1 & 2 PHYs provide independent general power-down and energy-detect power-down modes

which reduce PHY power consumption. General power-down mode provides power savings by

powering down the entire PHY, except the PHY management control interface. General power-down

mode must be manually enabled and disabled as described in Section 7.2.9.1, "PHY General Power-

Down," on page 95.

In energy-detect power-down mode, the PHY will resume from power-down when energy is seen on

the cable (typically from link pulses). If the ENERGYON interrupt (INT7) of either PHYs Port x PHY

Interrupt Mask Register (PHY_INTERRUPT_MASK_x) is unmasked, then the corresponding PHY will

generate an interrupt. These interrupts are reflected in the Interrupt Status Register (INT_STS) bit 27

(PHY_INT2) for the Port 2 PHY, and bit 26 (PHY_INT1) for the Port 1 PHY. These interrupts can be

used to trigger the IRQ interrupt output pin, as described in Section 5.2.3, "Ethernet PHY Interrupts,"

on page 52. Refer to Section 7.2.9.2, "PHY Energy Detect Power-Down," on page 95 for details on the

operation and configuration of the PHY energy-detect power-down mode.

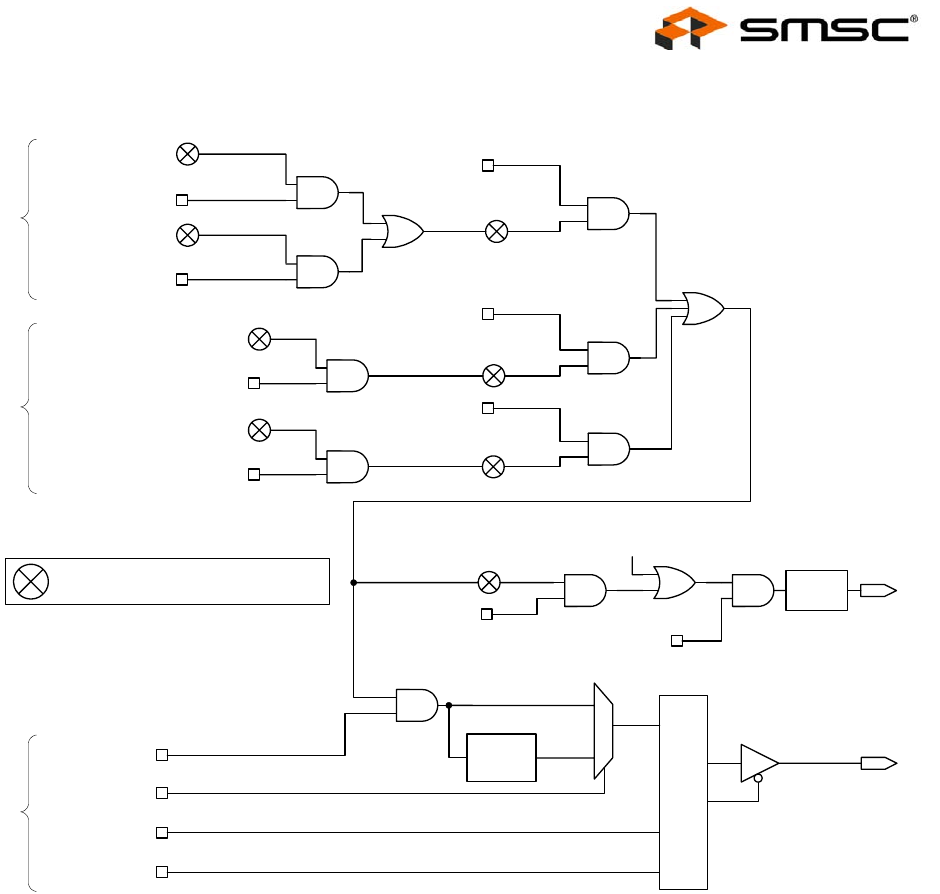

Figure 4.1 PME and PME_INT Signal Generation

PME

ED_EN1 (bit 14) of

PMT_CTRL register

WOL_EN (bit 9) of

PMT_CTRL register

50ms

PME_EN (bit 1) of

PMT_CTRL register

PME_IND (bit 3) of

PMT_CTRL register

PME_POL (bit 2) of

PMT_CTRL register

PME_TYPE (bit 6) of

PMT_CTRL register

LOGIC

WUEN (bit 2) of

HMAC_WUCSR register

MPEN (bit 1) of

HMAC_WUCSR register

WOL_STS (bit 5) of

PMT_CTRL register

WUFR (bit 6) of

HMAC_WUCSR register

MPR (bit 5) of

HMAC_WUCSR register

Denotes a level-triggered "sticky" status bit

PME_INT_EN (bit 17)

of INT_EN register

PME_INT (bit 17)

of INT_STS register

IRQ_EN (bit 8)

of IRQ_CFG register

IRQ

Other System

Interrupts

ED_STS1 (bit 16) of

PMT_CTRL register

ED_EN2 (bit 15) of

PMT_CTRL register

ED_STS2 (bit 17) of

PMT_CTRL register

Host MACPort 1 & 2 PHYs

Power Management Control

INT7_MASK (bit 7) of

PHY_INTERRUPT_SOURCE_1 register

INT7 (bit 7) of

PHY_INTERRUPT_SOURCE_1 register

INT7_MASK (bit 7) of

PHY_INTERRUPT_SOURCE_2 register

INT7 (bit 7) of

PHY_INTERRUPT_SOURCE_2 register

Polarity &

Buffer Type

Logic