Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 150 SMSC LAN9311/LAN9311i

DATASHEET

10.2.4 EEPROM Loader

The EEPROM Loader interfaces to the I

2

C/Microwire EEPROM controller, the PHYs, and to the system

CSRs (via the Register Access MUX). Only system CSRs at addresses 100h and above are accessible

to the EEPROM Loader (with the addition of the PHY Management Interface Data Register

(PMI_DATA) and PHY Management Interface Access Register (PMI_ACCESS) at addresses A4 and

A8 respectively).

The EEPROM Loader runs upon a pin reset (nRST), power-on reset (POR), digital reset

(DIGITAL_RST bit in the Reset Control Register (RESET_CTL)), or upon the issuance of a RELOAD

command via the EEPROM Command Register (E2P_CMD). A soft reset will run the EEPROM

Loader, but only the MAC address is loaded into the Host MAC. Refer to Section 4.2, "Resets," on

page 36 for additional information on the LAN9311/LAN9311i resets.

The EEPROM contents must be loaded in a specific format for use with the EEPROM Loader. An

overview of the EEPROM content format is shown in Table 10.7. Each section of EEPROM contents

is discussed in detail in the following sections.

10.2.4.1 EEPROM Loader Operation

Upon a pin reset (nRST), power-on reset (POR), digital reset (DIGITAL_RST bit in the Reset Control

Register (RESET_CTL)), or upon the issuance of a RELOAD command via the EEPROM Command

Register (E2P_CMD), the EPC_BUSY bit in the EEPROM Command Register (E2P_CMD) will be set.

While the EEPROM Loader is active, the READY bit of the Hardware Configuration Register

(HW_CFG) and Power Management Control Register (PMT_CTRL) is cleared and no writes to the

LAN9311/LAN9311i should be attempted. The operational flow of the EEPROM Loader can be seen

in Figure 10.14.

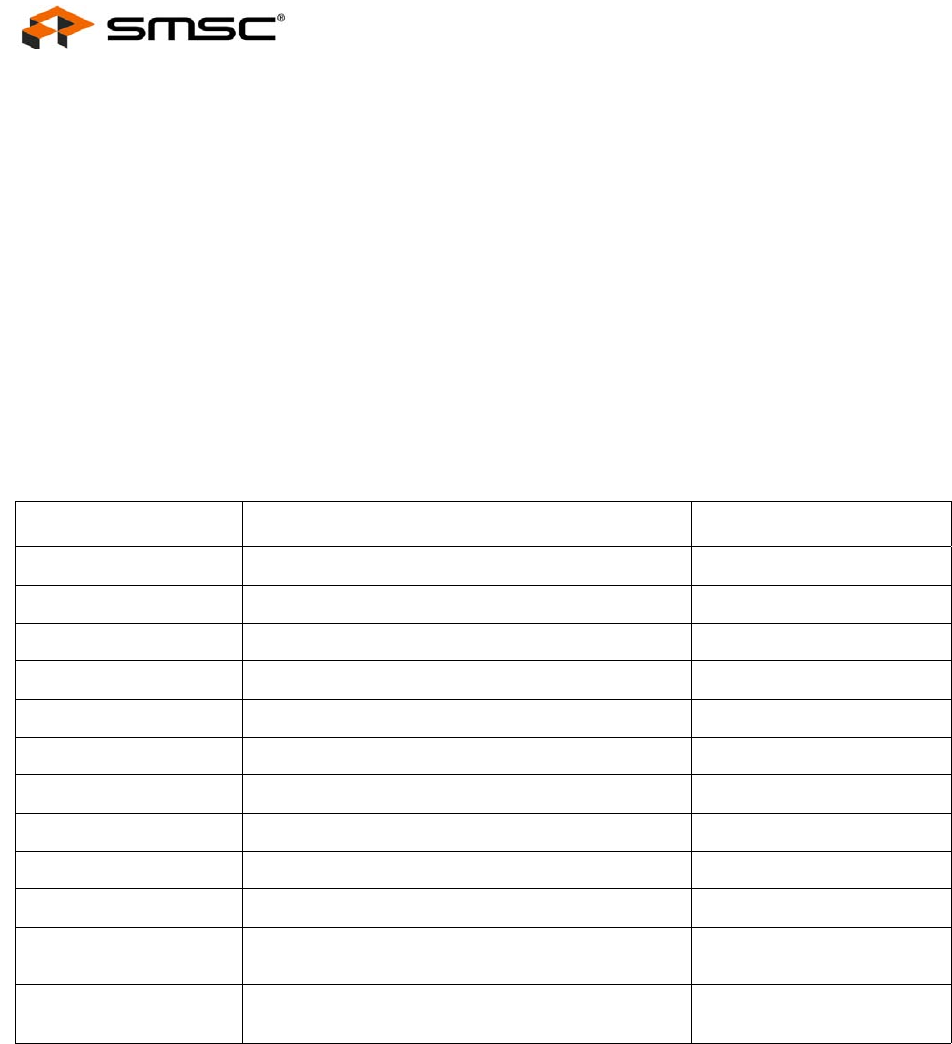

Table 10.7 EEPROM Contents Format Overview

EEPROM ADDRESS DESCRIPTION VALUE

0 EEPROM Valid Flag A5h

1 MAC Address Low Word [7:0] 1

st

Byte on the Network

2 MAC Address Low Word [15:8] 2

nd

Byte on the Network

3 MAC Address Low Word [23:16] 3

rd

Byte on the Network

4 MAC Address Low Word [31:24] 4

th

Byte on the Network

5 MAC Address High Word [7:0] 5

th

Byte on the Network

6 MAC Address High Word [15:8] 6

th

Byte on the Network

7 Configuration Strap Values Valid Flag A5h

8 - 11 Configuration Strap Values See Table 10.8

12 Burst Sequence Valid Flag A5h

13 Number of Bursts See Section 10.2.4.5,

"Register Data"

14 and above Burst Data See Section 10.2.4.5,

"Register Data"