Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 309 Revision 1.4 (08-19-08)

DATASHEET

14.5 Switch Fabric Control and Status Registers

This section details the various LAN9311/LAN9311i switch control and status registers that reside

within the switch fabric. The switch control and status registers allow configuration of each individual

switch port, the switch engine, and buffer manager. Switch fabric related interrupts and resets are also

controlled and monitored via the switch CSRs.

The switch CSRs are not memory mapped. All switch CSRs are accessed indirectly via the Switch

Fabric CSR Interface Command Register (SWITCH_CSR_CMD), Switch Fabric CSR Interface Data

Register (SWITCH_CSR_DATA), and Switch Fabric CSR Interface Direct Data Register

(SWITCH_CSR_DIRECT_DATA) in the system CSR memory mapped address space. All accesses to

the switch CSRs must be performed through these registers. Refer to Section 14.2.6, "Switch Fabric"

for additional information.

Note: The flow control settings of the switch ports are configured via the Switch Fabric registers: Port

1 Manual Flow Control Register (MANUAL_FC_1), Port 2 Manual Flow Control Register

(MANUAL_FC_2), and Port 0(Host MAC) Manual Flow Control Register (MANUAL_FC_MII)

located in the system CSR address space.

Table 14.12 lists the Switch CSRs and their corresponding addresses in order. The switch fabric

registers can be categorized into the following sub-sections:

Section 14.5.1, "General Switch CSRs," on page 320

Section 14.5.2, "Switch Port 0, Port 1, and Port 2 CSRs," on page 324

Section 14.5.3, "Switch Engine CSRs," on page 368

Section 14.5.4, "Buffer Manager CSRs," on page 413

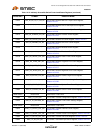

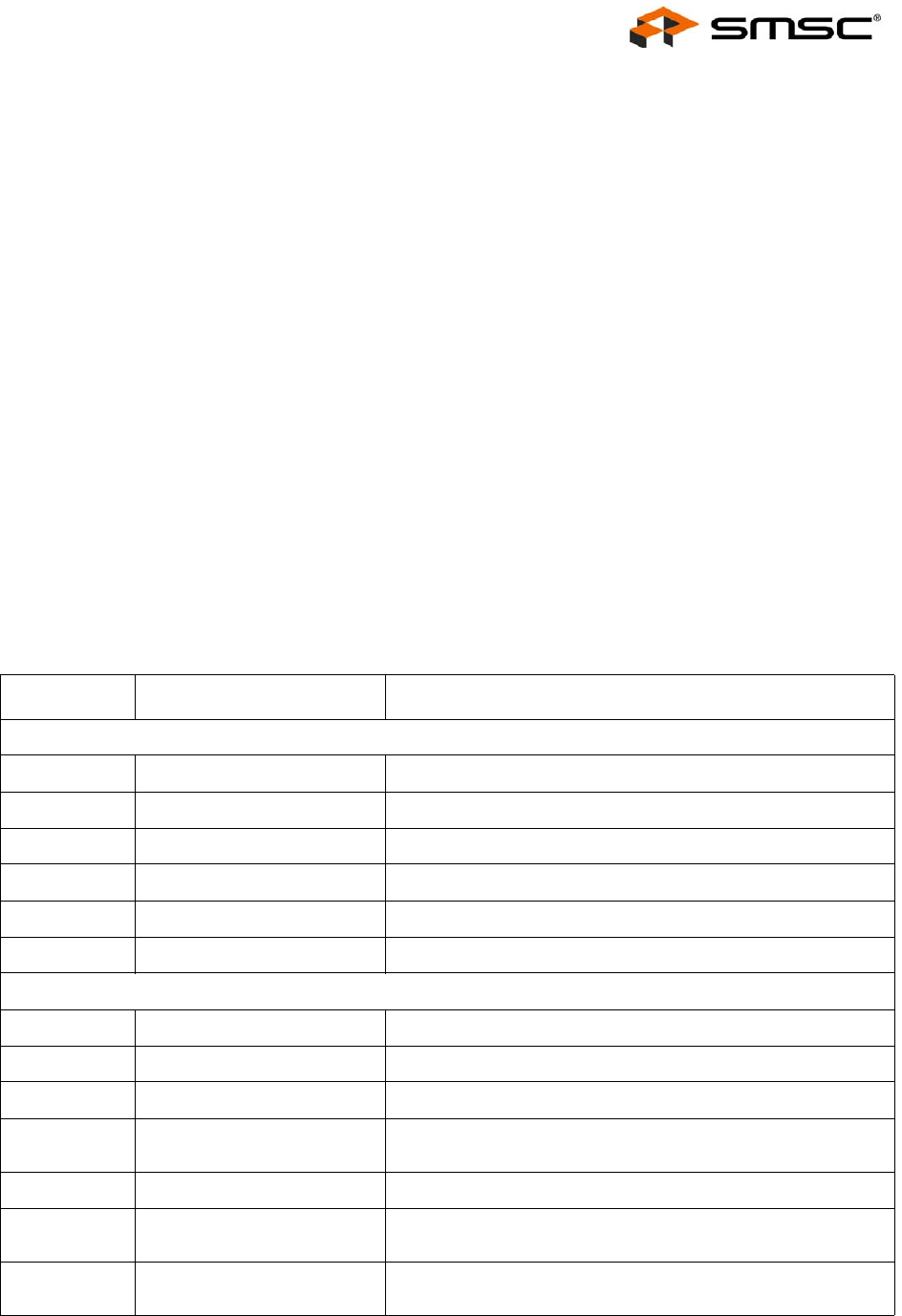

Table 14.12 Indirectly Accessible Switch Control and Status Registers

REGISTER # SYMBOL REGISTER NAME

General Switch CSRs

0000h SW_DEV_ID Switch Device ID Register, Section 14.5.1.1

0001h SW_RESET Switch Reset Register, Section 14.5.1.2

0002h-0003h RESERVED Reserved for Future Use

0004h SW_IMR Switch Global Interrupt Mask Register, Section 14.5.1.3

0005h SW_IPR Switch Global Interrupt Pending Register, Section 14.5.1.4

0006h-03FFh RESERVED Reserved for Future Use

Switch Port 0 CSRs

0400h MAC_VER_ID_MII Port 0 MAC Version ID Register, Section 14.5.2.1

0401h MAC_RX_CFG_MII Port 0 MAC Receive Configuration Register, Section 14.5.2.2

0402h-040Fh RESERVED Reserved for Future Use

0410h

MAC_RX_UNDSZE_CNT_MII

Port 0 MAC Receive Undersize Count Register,

Section 14.5.2.3

0411h MAC_RX_64_CNT_MII Port 0 MAC Receive 64 Byte Count Register, Section 14.5.2.4

0412h

MAC_RX_65_TO_127_CNT_MII

Port 0 MAC Receive 65 to 127 Byte Count Register,

Section 14.5.2.5

0413h

MAC_RX_128_TO_255_CNT_MII

Port 0 MAC Receive 128 to 255 Byte Count Register,

Section 14.5.2.6