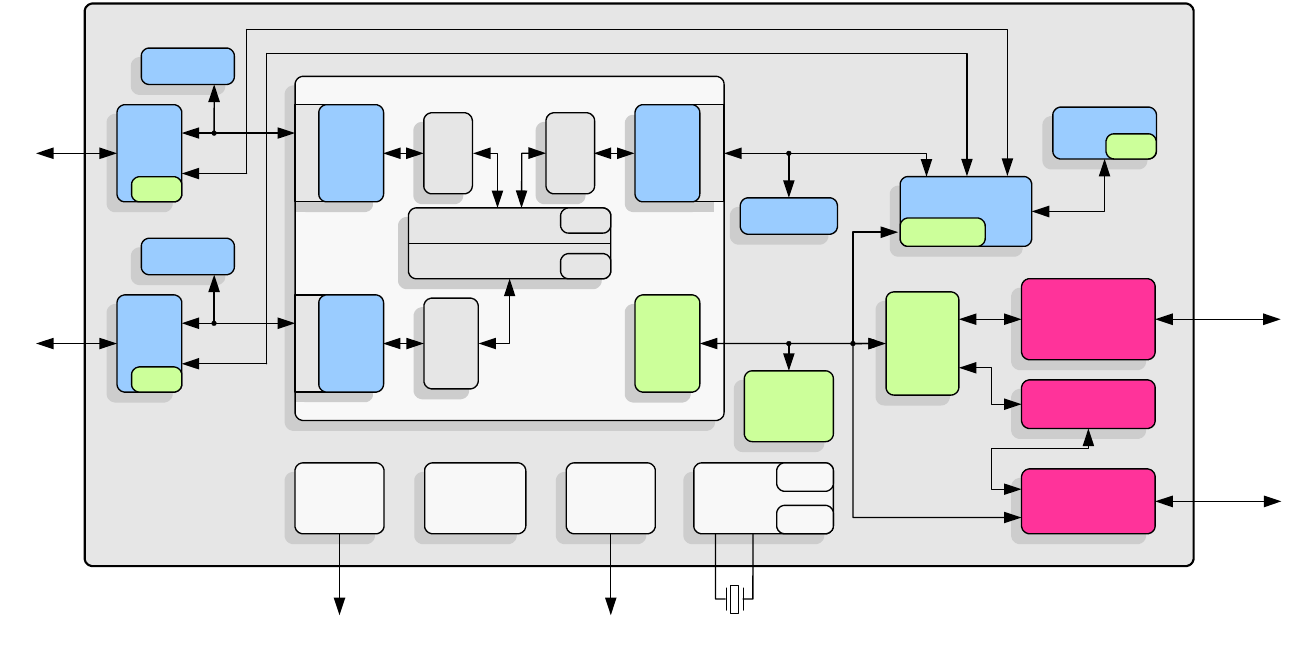

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 21 SMSC LAN9311/LAN9311i

DATASHEET

2.2 Block Diagram

Figure 2.1 Internal LAN9311/LAN9311i Block Diagram

To optional

EEPROM

EEPROM Controller

I

2

C (master)

Microwire (master)

EEPROM Loader

Register

Access

MUX

System

Registers

(CSRs)

I

2

C/Microwire

MII

IEEE 1588

Time Stamp

Registers

Virtual PHY

10/100

PHY

Registers

10/100

PHY

Registers

Switch

Registers

(CSRs)

IEEE 1588

Time Stamp

IEEE 1588

Time Stamp

Switch Fabric

GPIO/LED

Controller

Dynamic

QoS

4 Queues

Dynamic

QoS

4 Queues

Dynamic

QoS

4 Queues

Switch Engine

Buffer Manager

Search

Engine

Frame

Buffers

IEEE 1588

Time Stamp

Clock/Events

MII

MDIO

MII

MDIO

To optional GPIOs/LEDs

To Ethernet

To Ethernet

LAN9311/LAN9311i

Host Bus Interface

TX/RX FIFOs

Host MAC

To 16-bit

Host Bus

System

Interrupt

Controller

IRQ

GP Timer

Free-Run

Clk

System

Clocks/

Reset/PME

Controller

External

25MHz Crystal

MDIO

MDIO

MDIO

Port 0

10/100

MAC

Port 2

10/100

MAC

Port 1

10/100

MAC