Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 255 Revision 1.4 (08-19-08)

DATASHEET

14.2.8.6 Virtual PHY Auto-Negotiation Link Partner Base Page Ability Register (VPHY_AN_LP_BASE_ABILITY)

This read-only register contains the advertised ability of the link partner’s PHY and is used in the Auto-

Negotiation process with the Virtual PHY. Because the Virtual PHY does not physically connect to an

actual link partner, the values in this register are emulated as described below.

Offset:

Index (decimal):

1D4h

5

Size: 32 bits

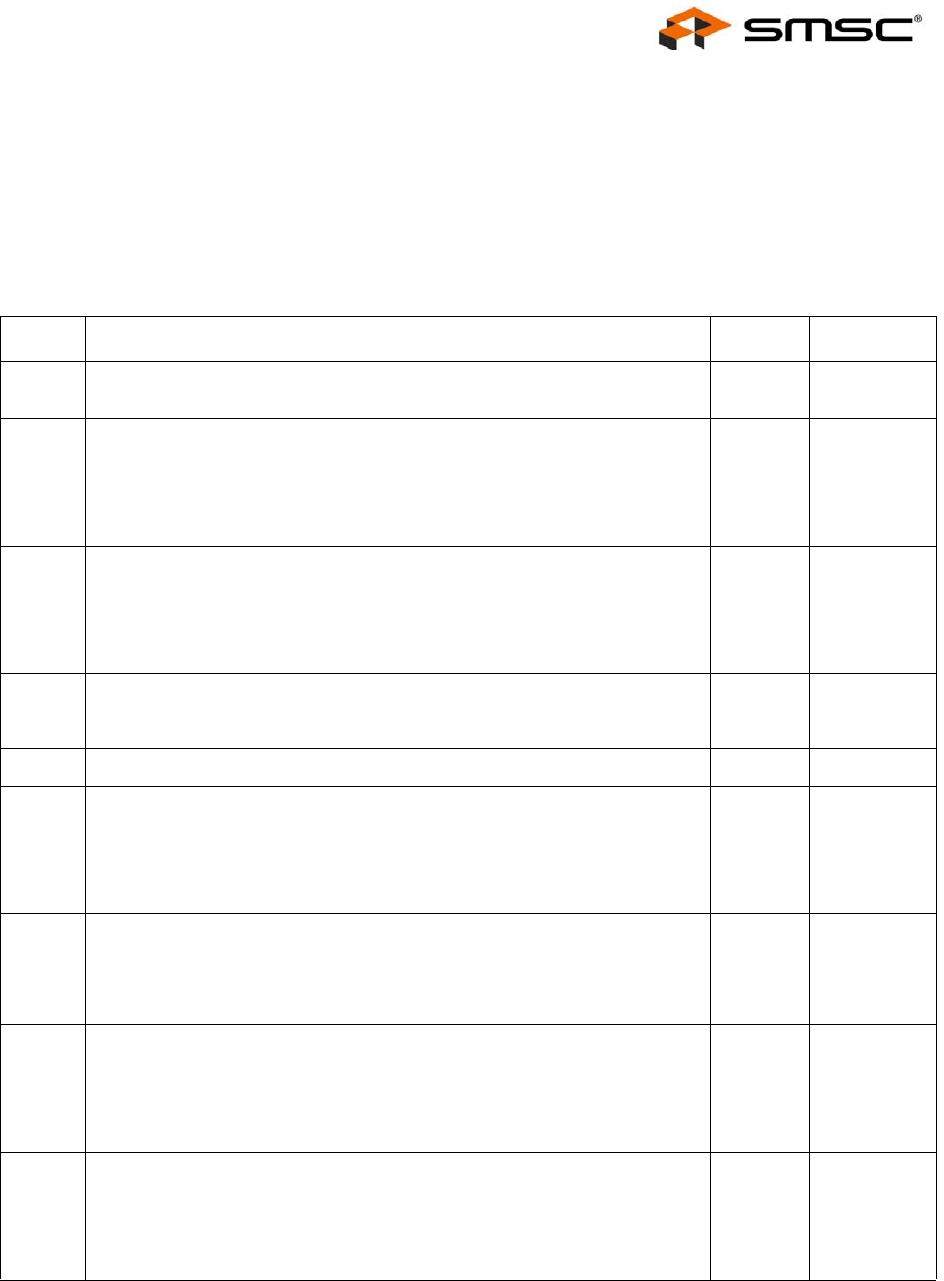

BITS DESCRIPTION TYPE DEFAULT

31:16 RESERVED

(See Note 14.33)

RO -

15

Next Page

This bit indicates the emulated link partner PHY next page capability and is

always 0.

0: Link partner PHY does not advertise next page capability

1: Link partner PHY advertises next page capability

RO 0b

Note 14.34

14

Acknowledge

This bit indicates whether the link code word has been received from the

partner and is always 1.

0: Link code word not yet received from partner

1: Link code word received from partner

RO 1b

Note 14.34

13

Remote Fault

Since there is no physical link partner, this bit is not used and is always

returned as 0.

RO 0b

Note 14.34

12

RESERVED RO -

11

Asymmetric Pause

This bit indicates the emulated link partner PHY asymmetric pause

capability.

0: No Asymmetric PAUSE toward link partner

1: Asymmetric PAUSE toward link partner

RO Note 14.35

10

Pause

This bit indicates the emulated link partner PHY symmetric pause capability.

0: No Symmetric PAUSE toward link partner

1: Symmetric PAUSE toward link partner

RO Note 14.35

9

100BASE-T4

This bit indicates the emulated link partner PHY 100BASE-T4 capability.

This bit is always 0.

0: 100BASE-T4 ability not supported

1: 100BASE-T4 ability supported

RO 0b

Note 14.34

8

100BASE-X Full Duplex

This bit indicates the emulated link partner PHY 100BASE-X full duplex

capability.

0: 100BASE-X full duplex ability not supported

1: 100BASE-X full duplex ability supported

RO Note 14.36