Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 256 SMSC LAN9311/LAN9311i

DATASHEET

Note 14.33 The reserved bits 31-16 are used to pad the register to 32-bits so that each register is on

a DWORD boundary. When accessed serially (through the MII management protocol), the

register is 16-bits wide.

Note 14.34 The emulated link partner does not support next page, always instantly sends its link code

word, never sends a fault, and does not support 100BASE-T4.

Note 14.35 The emulated link partner’s asymmetric/symmetric pause ability is based upon the values

of the Asymmetric Pause and Pause bits of the Virtual PHY Auto-Negotiation

Advertisement Register (VPHY_AN_ADV). Thus the emulated link partner always

accommodates the request of the Virtual PHY, as shown in Table 14.5. See Section 7.3.1,

"Virtual PHY Auto-Negotiation," on page 96 for additional information.

Note 14.36 The emulated link partner always has the following capabilities: 100BASE-X full duplex,

100BASE-X half duplex, 10BASE-T full duplex, and 10BASE-T half duplex. For more

information on the Virtual PHY auto-negotiation, see Section 7.3.1, "Virtual PHY Auto-

Negotiation," on page 96.

7

100BASE-X Half Duplex

This bit indicates the emulated link partner PHY 100BASE-X half duplex

capability.

0: 100BASE-X half duplex ability not supported

1: 100BASE-X half duplex ability supported

RO Note 14.36

6

10BASE-T Full Duplex

This bit indicates the emulated link partner PHY 10BASE-T full duplex

capability.

0: 10BASE-T full duplex ability not supported

1: 10BASE-T full duplex ability supported

RO Note 14.36

5

10BASE-T Half Duplex

This bit indicates the emulated link partner PHY 10BASE-T half duplex

capability.

0: 10BASE-T half duplex ability not supported

1: 10BASE-T half duplex ability supported

RO Note 14.36

4:0

Selector Field

This field identifies the type of message being sent by Auto-Negotiation.

00001: IEEE 802.3

RO 00001b

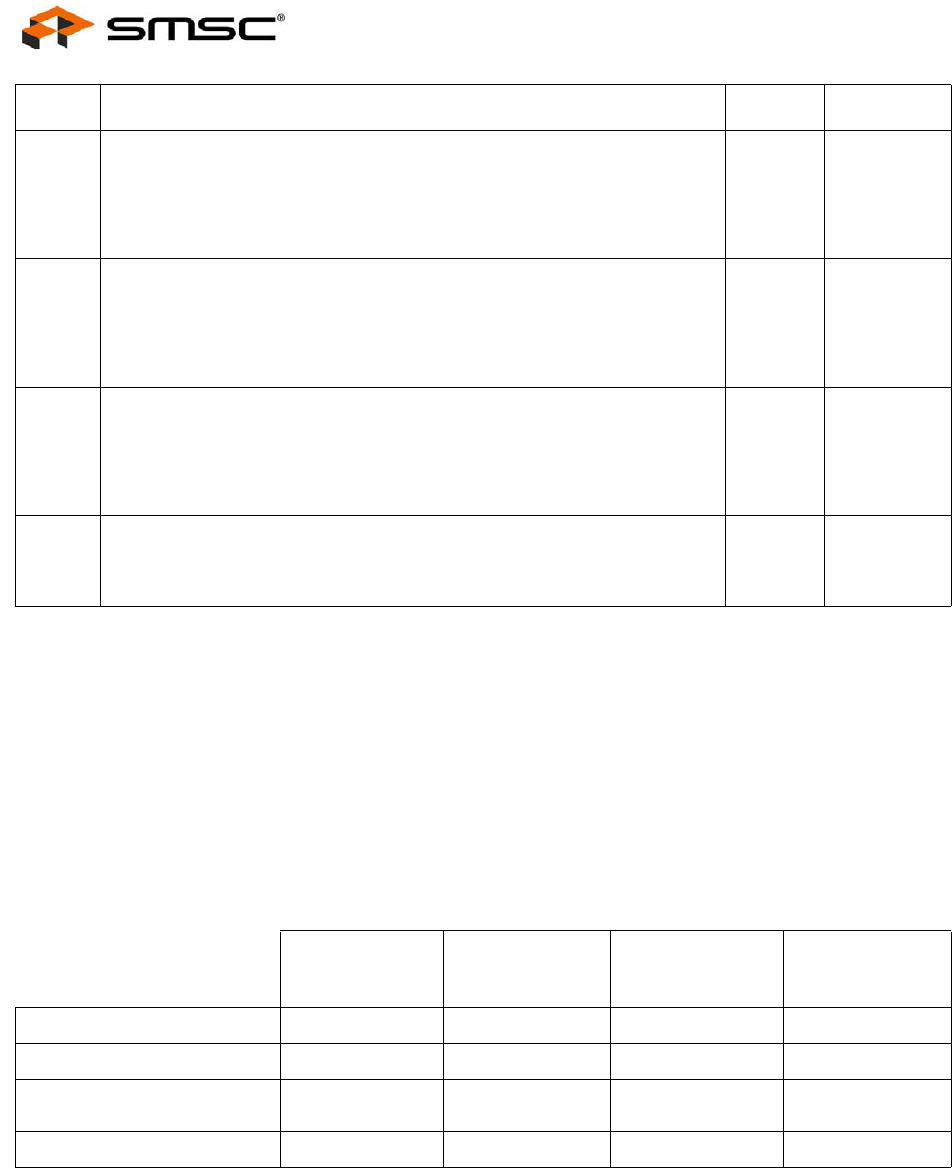

Table 14.5 Emulated Link Partner Pause Flow Control Ability Default Values

VPHY Symmetric

Pause

(register 4.10)

VPHY Asymmetric

Pause

(register 4.11)

Link Partner

Symmetric Pause

(register 5.10)

Link Partner

Asymmetric Pause

(register 5.11)

No Flow Control Enabled 0 0 0 0

Symmetric Pause 1 0 1 0

Asymmetric Pause Towards

Switch

01 1 1

Asymmetric Pause Towards MAC 1 1 0 1

BITS DESCRIPTION TYPE DEFAULT