Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 445 Revision 1.4 (08-19-08)

DATASHEET

Note 15.8 Measured at line side of transformer, line replaced by 100Ω (+/- 1%) resistor.

Note 15.9 Offset from 16nS pulse width at 50% of pulse peak.

Note 15.10 Measured differentially.

Note 15.11 Min/max voltages guaranteed as measured with 100Ω resistive load.

15.5 AC Specifications

This section details the various AC timing specifications of the LAN9311/LAN9311i.

Note: The I

2

C timing adheres to the Philips I

2

C-Bus Specification. Refer to the Philips I

2

C-Bus

Specification

for detailed I

2

C timing information.

15.5.1 Equivalent Test Load

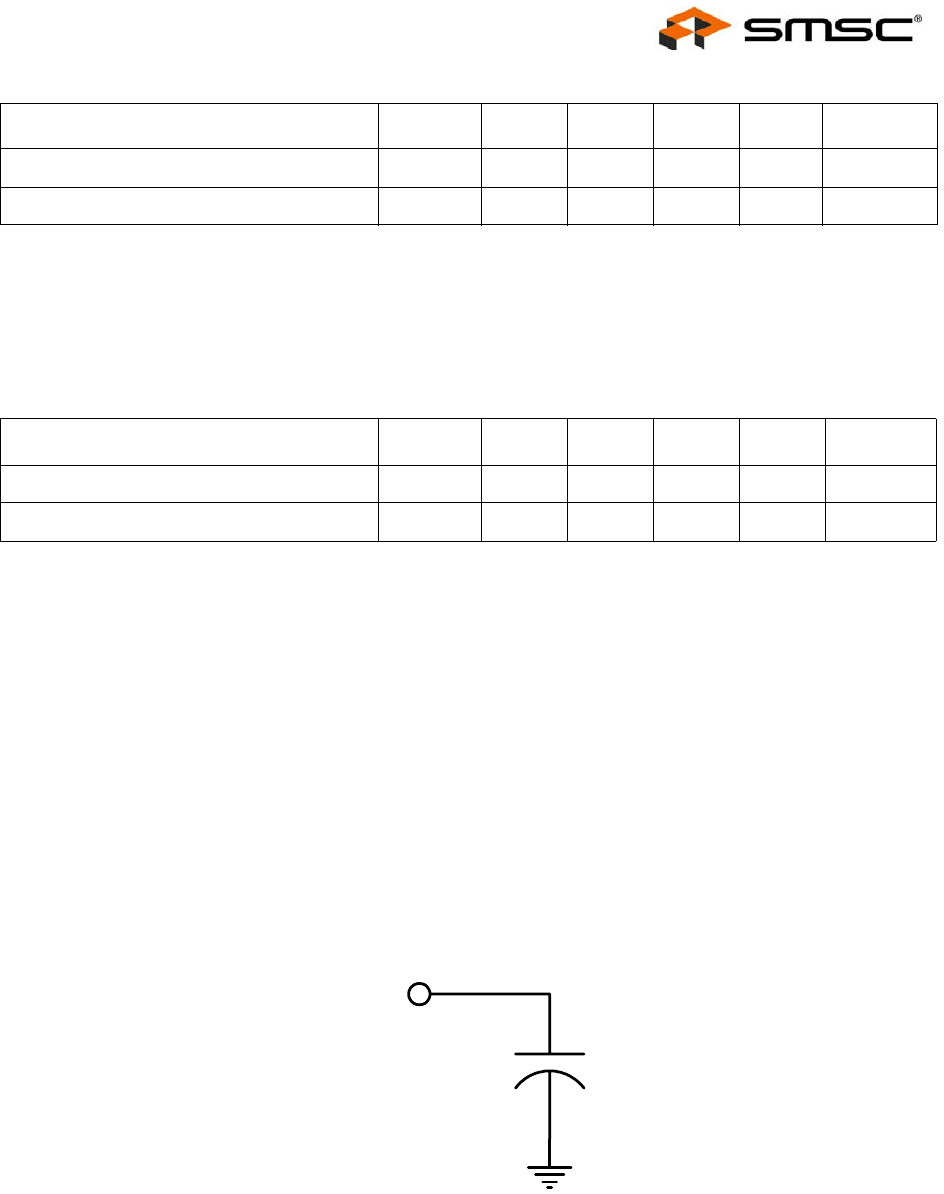

Output timing specifications assume the 25pF equivalent test load illustrated in Figure 15.1 below.

Overshoot and Undershoot V

OS

--5%

Jitter 1.4 nS

Note 15.10

Table 15.5 10BASE-T Transceiver Characteristics

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

Transmitter Peak Differential Output Voltage V

OUT

2.2 2.5 2.8 V

Note 15.11

Receiver Differential Squelch Threshold V

DS

300 420 585 mV

Figure 15.1 Output Equivalent Test Load

Table 15.4 100BASE-TX Transceiver Characteristics

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

25 pF

OUTPUT