Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 168 SMSC LAN9311/LAN9311i

DATASHEET

14.1 TX/RX FIFO Ports

The LAN9311/LAN9311i contains four host-accessible FIFO’s: TX Status, RX Status, TX Data, and RX

Data. These FIFO’s store the incoming and outgoing address and data information, acting as a conduit

between the host bus interface (HBI) and the Host MAC. The sizes of these FIFO’s are configurable

via the Hardware Configuration Register (HW_CFG). Refer to Section 9.7.3, "FIFO Memory Allocation

Configuration," on page 122 for additional information on FIFO size configuration.

For additional information on the FIFO configuration registers accessible via the Host Bus Interface,

refer to their respective register definitions located in section Section 14.2.2, "Host MAC & FIFO’s".

14.1.1 TX/RX Data FIFO’s

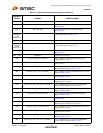

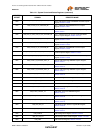

The TX and RX Data FIFO ports have the base address of 020h and 000h respectively. However, each

FIFO is also accessible at seven additional contiguous memory locations, as can be seen in

Figure 14.1. The Host may access the TX or RX Data FIFO’s at any of these alias port locations, as

they all function identically and contain the same data. This alias port addressing is implemented to

allow hosts to burst through sequential addresses.

14.1.2 TX/RX Status FIFO’s

The TX and RX Status FIFO’s can each be read from two register locations; the Status FIFO Port, and

the Status FIFO PEEK. The TX and RX Status FIFO Ports (048h and 040h respectively) will perform

a destructive read, popping the data from the TX or RX Status FIFO. The TX and RX Status FIFO

PEEK register locations (04Ch and 044h respectively) allow a non-destructive read of the top (oldest)

location of the FIFO’s.

14.1.3 Direct FIFO Access Mode

When the FIFO_SEL pin is driven high, the LAN9311/LAN9311i enters the direct FIFO access mode.

In this mode, all host write operations are to the TX Data FIFO and all host read operations are from

the RX Data FIFO. When FIFO_SEL is asserted, only the A[2:1] host address signals are decoded.

All other address signals are ignored in this mode. When the endianess select pin (END_SEL) is low,

the TX/RX Data FIFO’s are accessed in little endian mode. When END_SEL is high, the TX/RX Data

FIFO’s are accessed in big endian mode. The A[2:1] inputs are used during Data FIFO direct PIO burst

cycles to delimit WORD accesses. For more information on endianess selection, refer to section

Section 8.4, "Host Endianess".