Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 428 SMSC LAN9311/LAN9311i

DATASHEET

14.5.4.15 Buffer Manager Port 0 Egress Rate Priority Queue 2/3 Register (BM_EGRSS_RATE_02_03)

This register, along with the Buffer Manager Configuration Register (BM_CFG), is used to configure

the egress rate pacing.

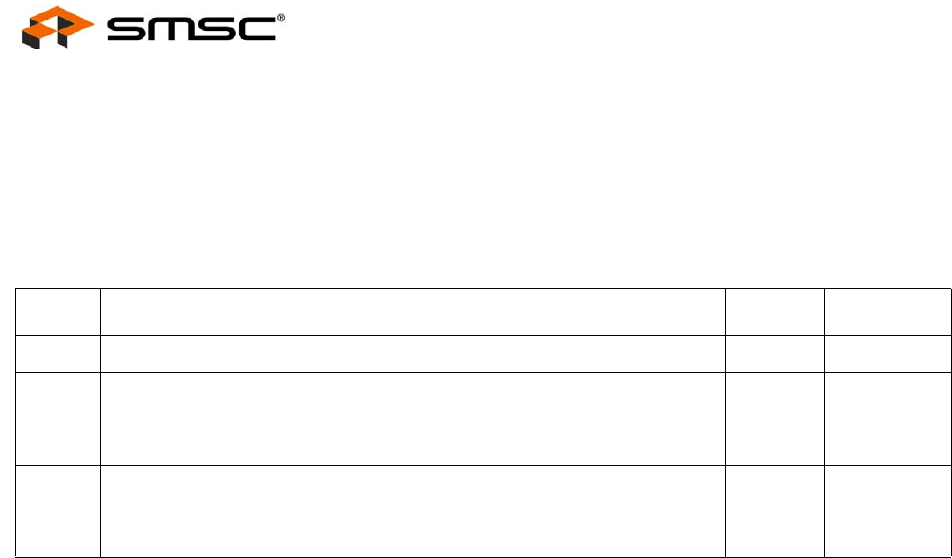

Register #: 1C0Eh Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:26 RESERVED RO -

25:13

Egress Rate Port 0 Priority Queue 3

These bits specify the egress data rate for the Port 0(Host MAC) priority

queue 3. The rate is specified in time per byte. The time is this value plus

1 times 20nS.

R/W 00000h

12:0

Egress Rate Port 0 Priority Queue 2

These bits specify the egress data rate for the Port 0(Host MAC) priority

queue 2. The rate is specified in time per byte. The time is this value plus

1 times 20nS.

R/W 00000h