Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 272 SMSC LAN9311/LAN9311i

DATASHEET

14.3.1 Host MAC Control Register (HMAC_CR)

This read/write register establishes the RX and TX operation modes and controls for address filtering

and packet filtering. Refer to Chapter 9, "Host MAC," on page 113 for additional information.

Bits 19-15, 13, and 11 determine if the Host MAC accepts the packets from the switch fabric. The

switch fabric address table and configuration determine which packets get sent to the Host MAC.

Offset: 1h Size: 32 bits

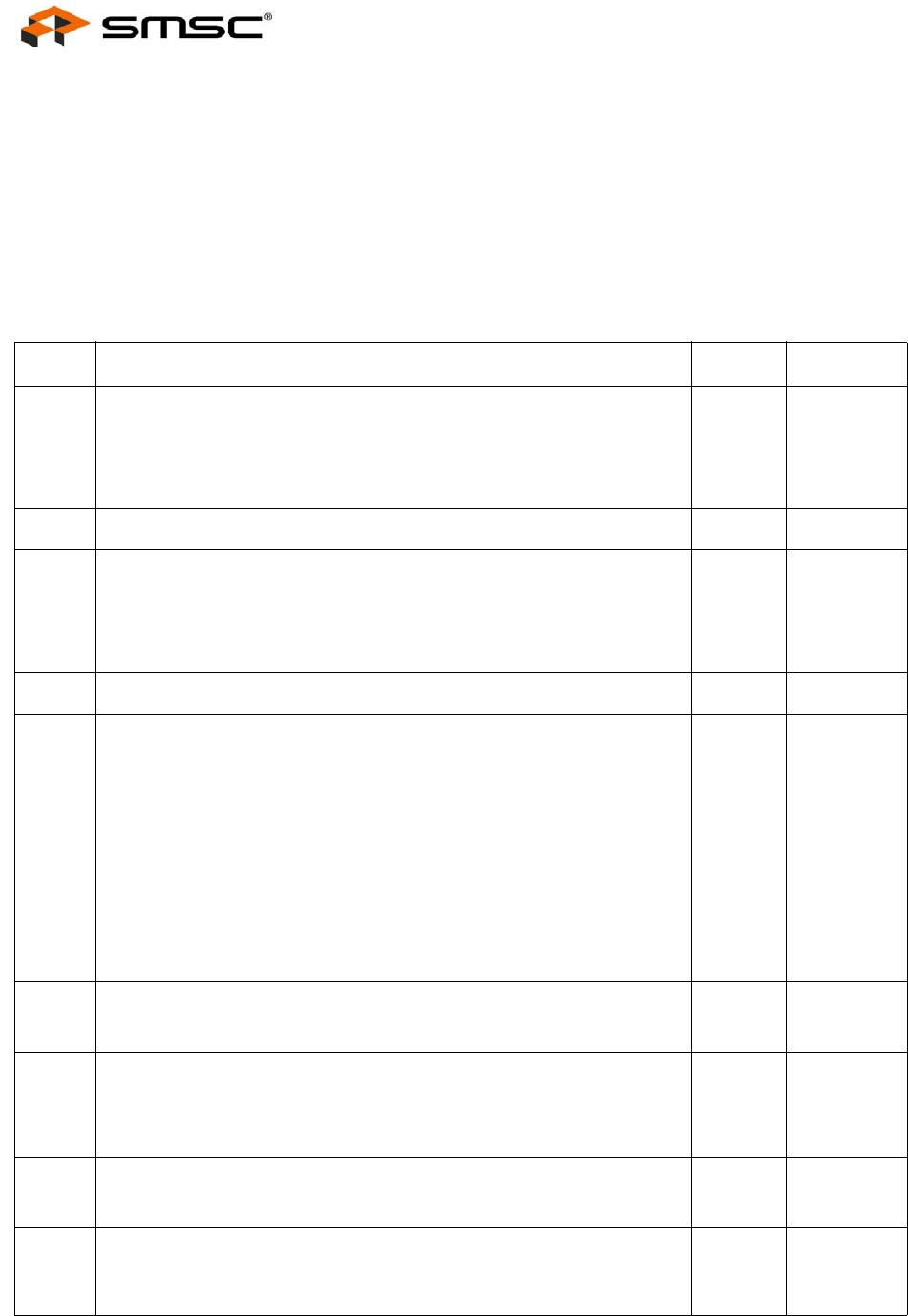

BITS DESCRIPTION TYPE DEFAULT

31 Receive All Mode (RXALL)

When set, all incoming packets will be received and passed on to the

address filtering function for processing of the selected filtering mode on the

received frame. Address filtering then occurs and is reported in Receive

Status. When cleared, only frames that pass Destination Address filtering

will be sent to the application.

R/W 0b

30:24

RESERVED RO -

23

Disable Receive Own (RCVOWN)

When set, the Host MAC disables the reception of frames when TXEN (bit

3) is asserted. The Host MAC blocks the transmitted frame on the receive

path. When cleared, the Host MAC receives all packets, including those

transmitted by the Host MAC. This bit should be cleared when the Full

Duplex Mode bit is set.

R/W 0b

22

RESERVED RO -

21 Loopback operation Mode (LOOPBK)

Selects the loop back operation modes for the Host MAC. This field is only

valid for full duplex mode. In internal loopback mode, the TX frame is

received by the internal MII interface, and sent back to the Host MAC

without being sent to the switch fabric.

0: Normal Operation. Loopback disabled.

1: Loopback enabled

Note:

When enabling or disabling the loopback mode it can take up to

10

μs for the mode change to occur. The transmitter and receiver

must be stopped and disabled when modifying the LOOPBK bit.

The transmitter or receiver should not be enabled within10μs of

modifying the LOOPBK bit.

R/W 0b

20

Full Duplex Mode (FDPX)

When set, the Host MAC operates in Full-Duplex mode, in which it can

transmit and receive simultaneously.

R/W 0b

19

Pass All Multicast (MCPAS)

When set, indicates that all incoming frames with a Multicast destination

address (first bit in the destination address field is 1) are received. Incoming

frames with physical address (Individual Address/Unicast) destinations are

filtered and received only if the address matches the Host MAC Address.

R/W 0b

18

Promiscuous Mode (PRMS)

When set, indicates that any incoming frame is received regardless of its

destination address.

R/W 1b

17

Inverse filtering (INVFILT)

When set, the address check function operates in inverse filtering mode.

This is valid only during Perfect filtering mode. Refer to Section 9.4.4,

"Inverse Filtering," on page 117 for additional information.

R/W 0b