Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 173 Revision 1.4 (08-19-08)

DATASHEET

14.2.1 Interrupts

This section details the interrupt related System CSR’s. These registers control, configure, and monitor

the IRQ interrupt output pin and the various LAN9311/LAN9311i interrupt sources. For more

information on the LAN9311/LAN9311i interrupts, refer to Chapter 5, "System Interrupts," on page 49.

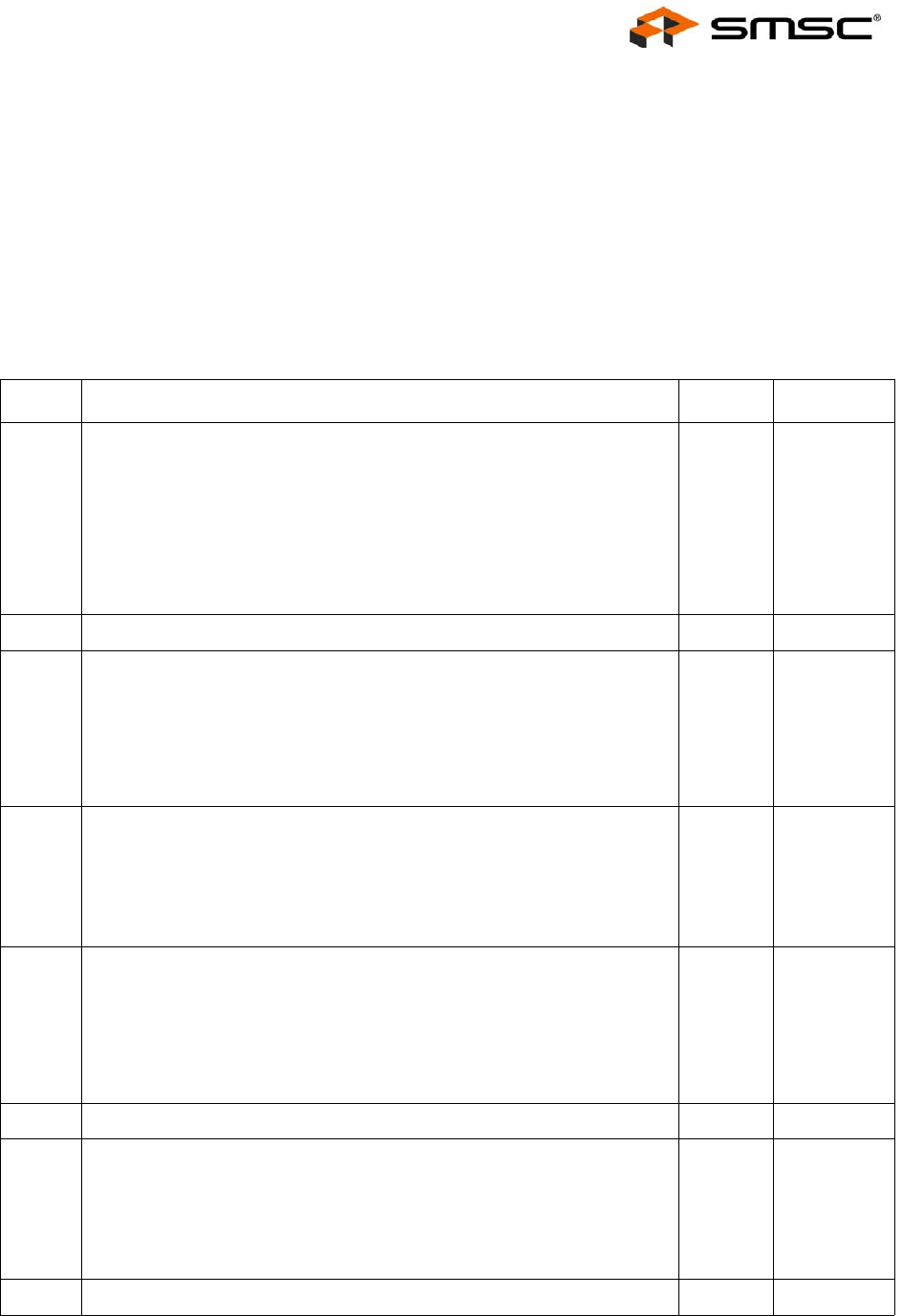

14.2.1.1 Interrupt Configuration Register (IRQ_CFG)

This read/write register configures and indicates the state of the IRQ signal.

Offset: 054h Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:24 Interrupt De-assertion Interval (INT_DEAS)

This field determines the Interrupt Request De-assertion Interval in multiples

of 10 microseconds.

Setting this field to zero causes the device to disable the INT_DEAS Interval,

reset the interval counter and issue any pending interrupts. If a new, non-

zero value is written to this field, any subsequent interrupts will obey the new

setting.

This field does not apply to the PME_INT interrupt.

R/W 00h

23:15

RESERVED RO -

14

Interrupt De-assertion Interval Clear (INT_DEAS_CLR)

Writing a 1 to this register clears the de-assertion counter in the Interrupt

Controller, thus causing a new de-assertion interval to begin (regardless of

whether or not the Interrupt Controller is currently in an active de-assertion

interval).

0: Normal operation

1: Clear de-assertion counter

R/W

SC

0h

13

Interrupt De-assertion Status (INT_DEAS_STS)

When set, this bit indicates that interrupts are currently in a de-assertion

interval, and will not be sent to the IRQ pin. When this bit is clear, interrupts

are not currently in a de-assertion interval, and will be sent to the IRQ pin.

0: No interrupts in de-assertion interval

1: Interrupts in de-assertion interval

RO

SC

0b

12

Master Interrupt (IRQ_INT)

This read-only bit indicates the state of the internal IRQ line, regardless of

the setting of the IRQ_EN bit, or the state of the interrupt de-assertion

function. When this bit is set, one of the enabled interrupts is currently

active.

0: No enabled interrupts active

1: One or more enabled interrupts active

RO 0b

11:9

RESERVED RO -

8

IRQ Enable (IRQ_EN)

This bit controls the final interrupt output to the IRQ pin. When clear, the IRQ

output is disabled and permanently de-asserted. This bit has no effect on

any internal interrupt status bits.

0: Disable output on IRQ pin

1: Enable output on IRQ pin

R/W 0b

7:5

RESERVED RO -