Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 249 Revision 1.4 (08-19-08)

DATASHEET

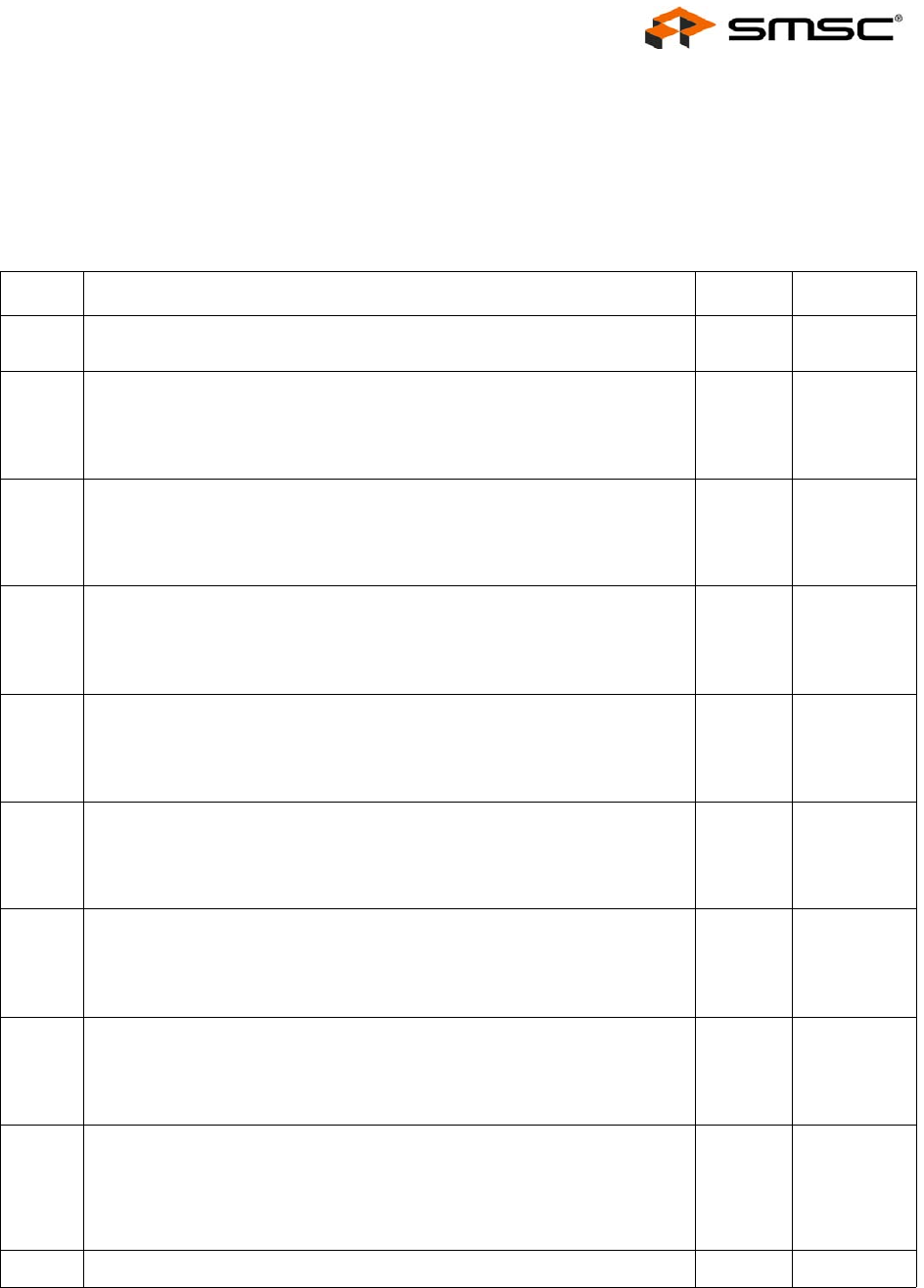

14.2.8.2 Virtual PHY Basic Status Register (VPHY_BASIC_STATUS)

This register is used to monitor the status of the Virtual PHY.

Offset:

Index (decimal):

1C4h

1

Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:16 RESERVED

(See Note 14.17)

RO -

15

100BASE-T4

This bit displays the status of 100BASE-T4 compatibility.

0: PHY not able to perform 100BASE-T4

1: PHY able to perform 100BASE-T4

RO 0b

Note 14.18

14

100BASE-X Full Duplex

This bit displays the status of 100BASE-X full duplex compatibility.

0: PHY not able to perform 100BASE-X full duplex

1: PHY able to perform 100BASE-X full duplex

RO 1b

13

100BASE-X Half Duplex

This bit displays the status of 100BASE-X half duplex compatibility.

0: PHY not able to perform 100BASE-X half duplex

1: PHY able to perform 100BASE-X half duplex

RO 1b

12

10BASE-T Full Duplex

This bit displays the status of 10BASE-T full duplex compatibility.

0: PHY not able to perform 10BASE-T full duplex

1: PHY able to perform 10BASE-T full duplex

RO 1b

11

10BASE-T Half Duplex

This bit displays the status of 10BASE-T half duplex compatibility.

0: PHY not able to perform 10BASE-T half duplex

1: PHY able to perform 10BASE-T half duplex

RO 1b

10

100BASE-T2 Full Duplex

This bit displays the status of 100BASE-T2 full duplex compatibility.

0: PHY not able to perform 100BASE-T2 full duplex

1: PHY able to perform 100BASE-T2 full duplex

RO 0b

Note 14.18

9

100BASE-T2 Half Duplex

This bit displays the status of 100BASE-T2 half duplex compatibility.

0: PHY not able to perform 100BASE-T2 half duplex

1: PHY able to perform 100BASE-T2 half duplex

RO 0b

Note 14.18

8

Extended Status

This bit displays whether extended status information is in register 15 (per

IEEE 802.3 clause 22.2.4).

0: No extended status information in Register 15

1: Extended status information in Register 15

RO 0b

Note 14.19

7

RESERVED RO -