Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 190 SMSC LAN9311/LAN9311i

DATASHEET

14.2.2.9 Host MAC Automatic Flow Control Configuration Register (AFC_CFG)

This read/write register configures the mechanism that controls the automatic and software-initiated

transmission of pause frames and back pressure from the Host MAC to the switch fabric. This register

is used in conjunction with the Host MAC Flow Control Register (HMAC_FLOW) in the Host MAC CSR

space. Pause frames and backpressure are sent to the switch fabric to stop it from sending packets

to the Host MAC. Network data into the switch fabric is affected only if the switch fabric buffering fills.

Note: The Host MAC will not transmit pause frames or assert back pressure if the transmitter is

disabled. This register controls only the Host MAC flow control and not the Switch Engine

MAC’s flow control.

Refer to section Section 9.2, "Flow Control" for additional information.

Offset: 0ACh Size: 32 bits

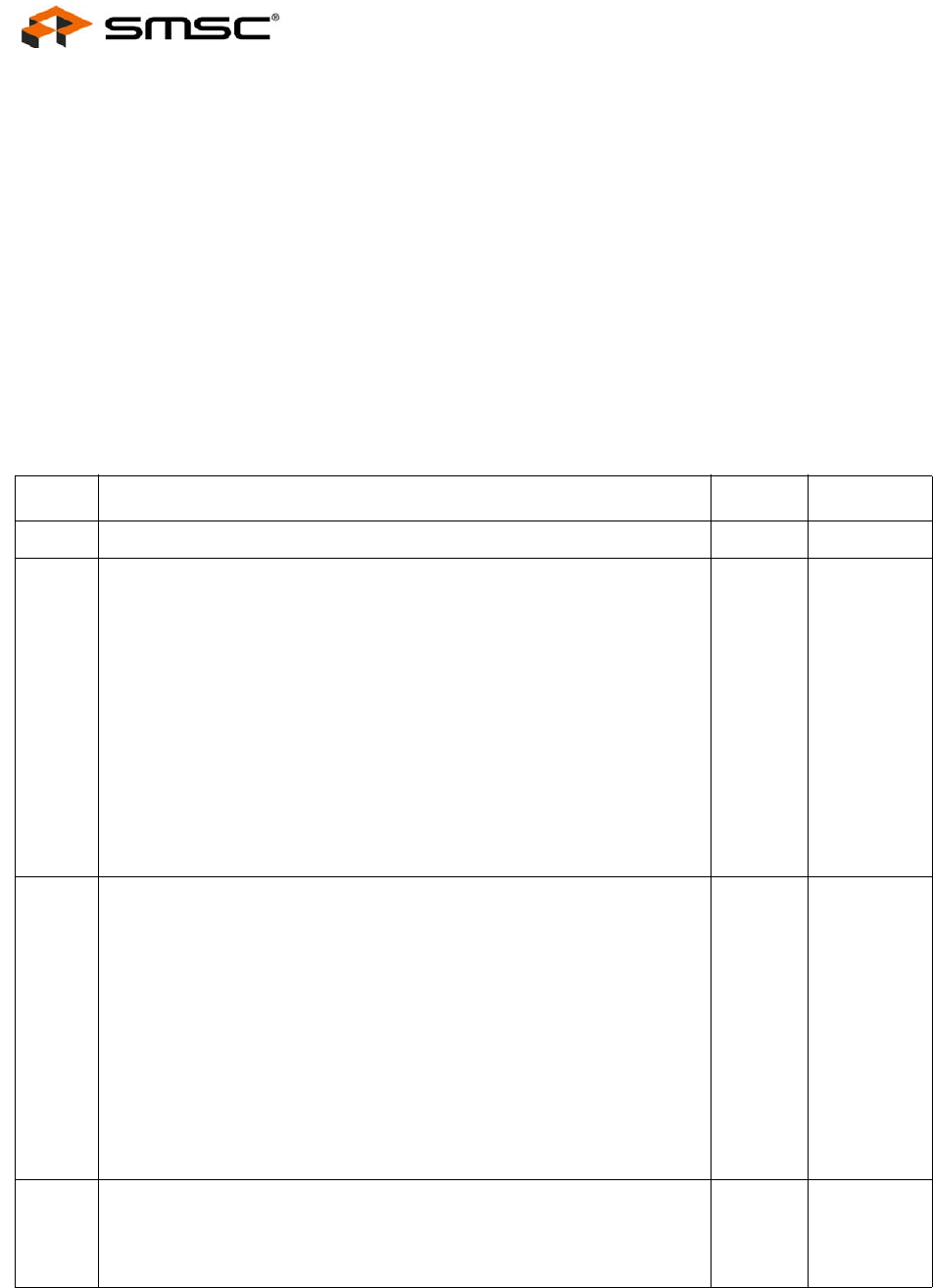

BITS DESCRIPTION TYPE DEFAULT

31:24 RESERVED RO -

23:16

Automatic Flow Control High Level (AFC_HI)

This field specifies, in multiples of 64 bytes, the level at which flow control

will trigger. When this limit is reached, the chip will apply back pressure or

will transmit a pause frame as programmed in bits [3:0] of this register.

During full-duplex operation only a single pause frame is transmitted when

this level is reached. The pause time transmitted in this frame is

programmed in the FCPT field of the Host MAC Flow Control Register

(HMAC_FLOW) in the Host MAC CSR space.

During half-duplex operation each incoming frame that matches the criteria

in bits [3:0] of this register will be jammed for the period set in the

BACK_DUR field.

Note: This level is also used for hard-wired flow control when

HW_FC_EN is set in the Port 0(Host MAC) Manual Flow Control

Register (MANUAL_FC_MII).

R/W 00h

15:8

Automatic Flow Control Low Level (AFC_LO)

This field specifies, in multiples of 64 bytes, the level at which a pause frame

is transmitted with a pause time setting of zero. When the amount of data

in the RX Data FIFO falls below this level the pause frame is transmitted. A

pause time value of zero instructs the other transmitting device to

immediately resume transmission. The zero time pause frame will only be

transmitted if the RX Data FIFO had reached the AFC_HI level and a pause

frame was sent. A zero pause time frame is sent whenever automatic flow

control in enabled in bits [3:0] of this register.

Note: When automatic flow control is enabled the AFC_LO setting must

always be less than the AFC_HI setting.

Note: This level is also used for hard-wired flow control when

HW_FC_EN is set in the Port 0(Host MAC) Manual Flow Control

Register (MANUAL_FC_MII).

R/W 00h

7:4

Backpressure Duration (BACK_DUR)

When the Host MAC automatically asserts back pressure, it will be asserted

for this period of time. In full-duplex mode, this field has no function and is

not used. Please refer to Table 14.2, describing Backpressure Duration bit

mapping for more information.

R/W 0h