Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 237 Revision 1.4 (08-19-08)

DATASHEET

14.2.6.5 Switch Fabric CSR Interface Command Register (SWITCH_CSR_CMD)

This read/write register is used in conjunction with the Switch Fabric CSR Interface Data Register

(SWITCH_CSR_DATA) to control the read and write operations to the various Switch Fabric CSR’s.

Refer to Section 14.5, "Switch Fabric Control and Status Registers," on page 309 for details on the

registers indirectly accessible via this register.

Offset: 1B0h Size: 32 bits

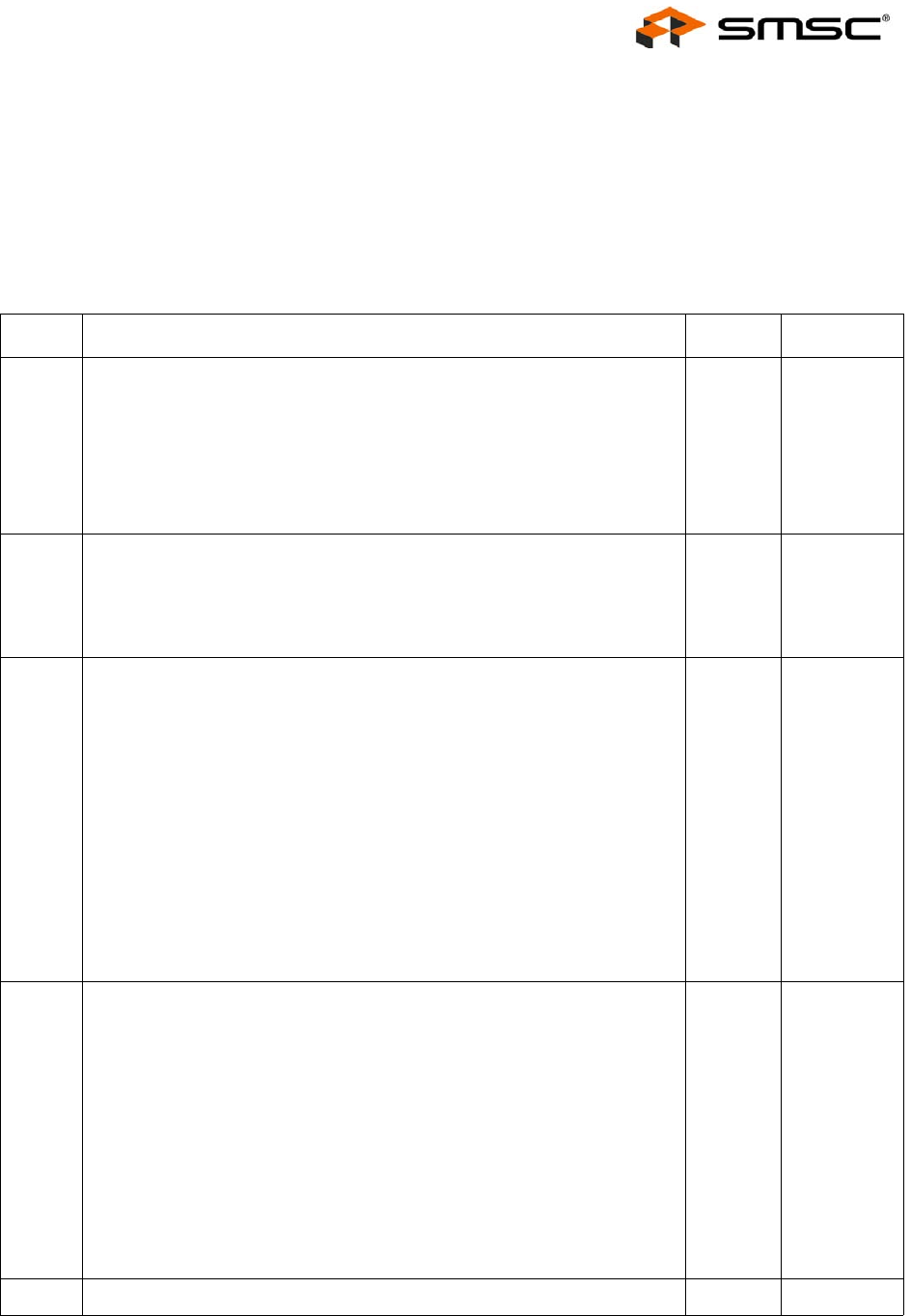

BITS DESCRIPTION TYPE DEFAULT

31 CSR Busy (CSR_BUSY)

When a 1 is written to this bit, the read or write operation (as determined by

the R_nW bit) is performed to the specified Switch Fabric CSR in CSR

Address (CSR_ADDR[15:0]). This bit will remain set until the operation is

complete, at which time the bit will clear. In the case of a read, the clearing

of this bit indicates to the Host that valid data can be read from the Switch

Fabric CSR Interface Data Register (SWITCH_CSR_DATA). The

SWITCH_CSR_CMD and SWITCH_CSR_DATA registers should not be

modified until this bit is cleared.

R/W

SC

0b

30

Read/Write (R_nW)

This bit determines whether a read or write operation is performed by the

Host to the specified Switch Engine CSR.

0: Write

1: Read

R/W 0b

29

Auto Increment (AUTO_INC)

This bit enables/disables the auto increment feature.

When this bit is set, a write to the Switch Fabric CSR Interface Data Register

(SWITCH_CSR_DATA) register will automatically set the CSR Busy

(CSR_BUSY) bit. Once the write command is finished, the CSR Address

(CSR_ADDR[15:0]) will automatically increment.

When this bit is set, a read from the Switch Fabric CSR Interface Data

Register (SWITCH_CSR_DATA) will automatically increment the CSR

Address (CSR_ADDR[15:0]) and set the CSR Busy (CSR_BUSY) bit. This

bit should be cleared by software before the last read from the

SWITCH_CSR_DATA register.

0: Disable Auto Increment

1: Enable Auto Increment

Note:

This bit has precedence over the Auto Decrement (AUTO_DEC) bit

R/W 0b

28

Auto Decrement (AUTO_DEC)

This bit enables/disables the auto decrement feature.

When this bit is set, a write to the Switch Fabric CSR Interface Data Register

(SWITCH_CSR_DATA) will automatically set the CSR Busy (CSR_BUSY)

bit. Once the write command is finished, the CSR Address

(CSR_ADDR[15:0]) will automatically decrement.

When this bit is set, a read from the Switch Fabric CSR Interface Data

Register (SWITCH_CSR_DATA) will automatically decrement the CSR

Address (CSR_ADDR[15:0]) and set the CSR Busy (CSR_BUSY) bit. This

bit should be cleared by software before the last read from the

SWITCH_CSR_DATA register.

0: Disable Auto Decrement

1: Enable Auto Decrement

R/W 0b

27:20

RESERVED RO -