Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 279 Revision 1.4 (08-19-08)

DATASHEET

14.3.6 Host MAC MII Access Register (HMAC_MII_ACC)

This read/write register is used in conjunction with the Host MAC MII Data Register (HMAC_MII_DATA)

to access the internal PHY registers. Refer to Section 14.4, "Ethernet PHY Control and Status

Registers" for a list of accessible PHY registers and PHY address information.

Offset: 6h Size: 32 bits

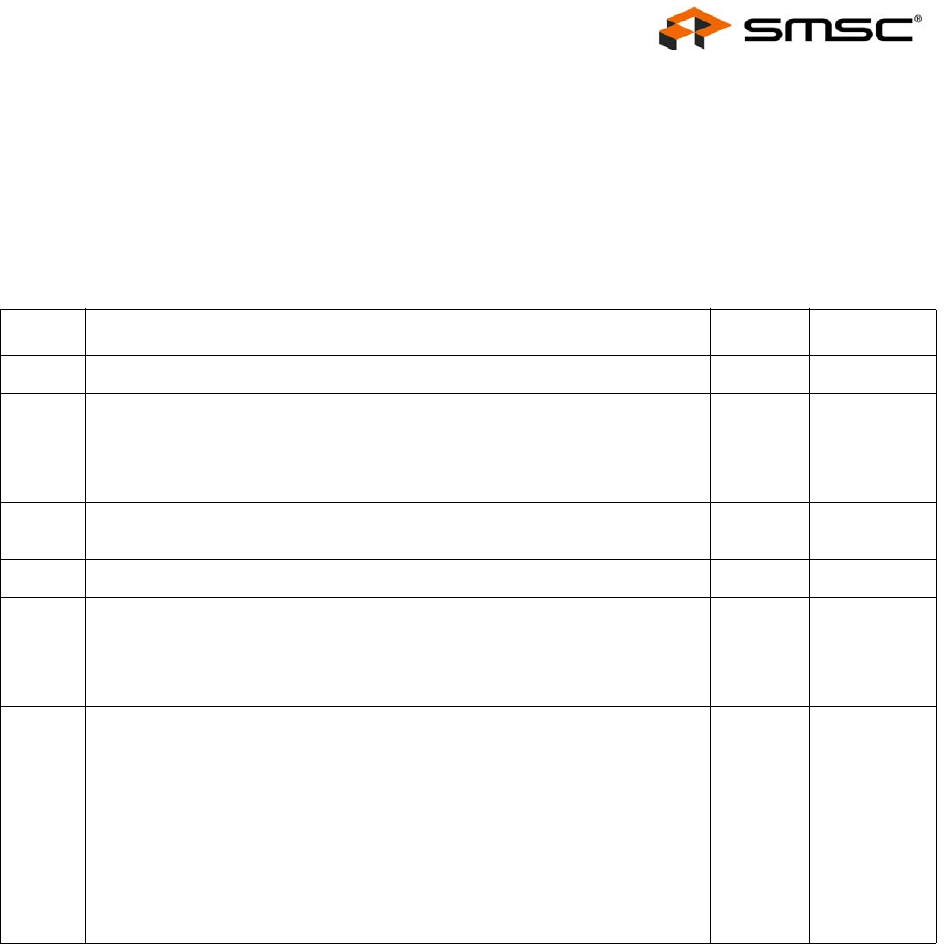

BITS DESCRIPTION TYPE DEFAULT

31:16 RESERVED RO -

15:11

PHY Address (PHY_ADDR)

This field must be loaded with the PHY address that the MII access is

intended for. A list default PHY addresses can be seen in Table 7.1. Refer

to Section 7.1.1, "PHY Addressing," on page 82 for additional information on

PHY addressing.

R/W 00000b

10:6

MII Register Index (MIIRINDA)

These bits select the desired MII register in the PHY.

R/W 00000b

5:2

RESERVED RO -

1

MII Write (MIIWnR)

Setting this bit tells the PHY that this will be a write operation using the Host

MAC MII Data Register (HMAC_MII_DATA). If this bit is cleared, a read

operation will occur, packing the data in the Host MAC MII Data Register

(HMAC_MII_DATA).

R/W 0b

0

MII Busy (MIIBZY)

This bit must be polled to determine when the MII register access is

complete. This bit must read a logical 0 before writing to this register or the

Host MAC MII Data Register (HMAC_MII_DATA).

The LAN driver software must set this bit in order for the

LAN9311/LAN9311i to read or write any of the MII PHY registers.

During a MII register access, this bit will be set, signifying a read or write

access is in progress. The MII data register must be kept valid until the Host

MAC clears this bit during a PHY write operation. The MII data register is

invalid until the Host MAC has cleared this bit during a PHY read operation.

R/W

SC

0b