Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 119 Revision 1.4 (08-19-08)

DATASHEET

The Filter i Offset register defines the offset in the frame’s destination address field from which the

frames are examined by Filter i. Table 9.5 describes the Filter i Offset bit fields.

The Filter i CRC-16 register contains the CRC-16 result of the frame that should pass Filter i.

Table 9.6 describes the Filter i CRC-16 bit fields.

9.5.1 Magic Packet Detection

Setting the Magic Packet Enable bit (MPEN) in the Host MAC Wake-up Control and Status Register

(HMAC_WUCSR) places the Host MAC in the “Magic Packet” detection mode. In this mode, normal

data reception is disabled, and detection logic within the Host MAC examines received data for a Magic

Packet. The LAN9311/LAN9311i can be programmed to notify the host of the “Magic Packet” detection

with the assertion of the host interrupt (IRQ) or power management event signal (PME). Upon

detection, the Magic Packet Received bit (MPR) in the HMAC_WUCSR register is set. When the host

clears the MPEN bit, the Host MAC will resume normal receive operation. Please refer to Section

14.3.12, "Host MAC Wake-up Control and Status Register (HMAC_WUCSR)," on page 286 for

additional information on this register.

In Magic Packet mode, the Host MAC constantly monitors each frame addressed to the node for a

specific Magic Packet pattern. Only packets matching the Host MAC address or broadcast address are

checked for the Magic Packet requirements. Once the address requirement has been met, the Host

MAC checks the received frame for the pattern 48’hFF_FF_FF_FF_FF_FF after the destination and

source address field. The Host MAC then looks in the frame for 16 repetitions of the Host MAC address

without any breaks or interruptions. In case of a break in the 16 address repetitions, the Host MAC

again scans for the 48'hFF_FF_FF_FF_FF_FF pattern in the incoming frame. The 16 repetitions may

be anywhere in the frame but must be preceded by the synchronization stream. The device will also

accept a multicast frame, as long as it detects the 16 duplications of the Host MAC address.

For example, if the Host MAC address is 00h 11h 22h 33h 44h 55h, then the MAC scans for the

following data sequence in an Ethernet frame:

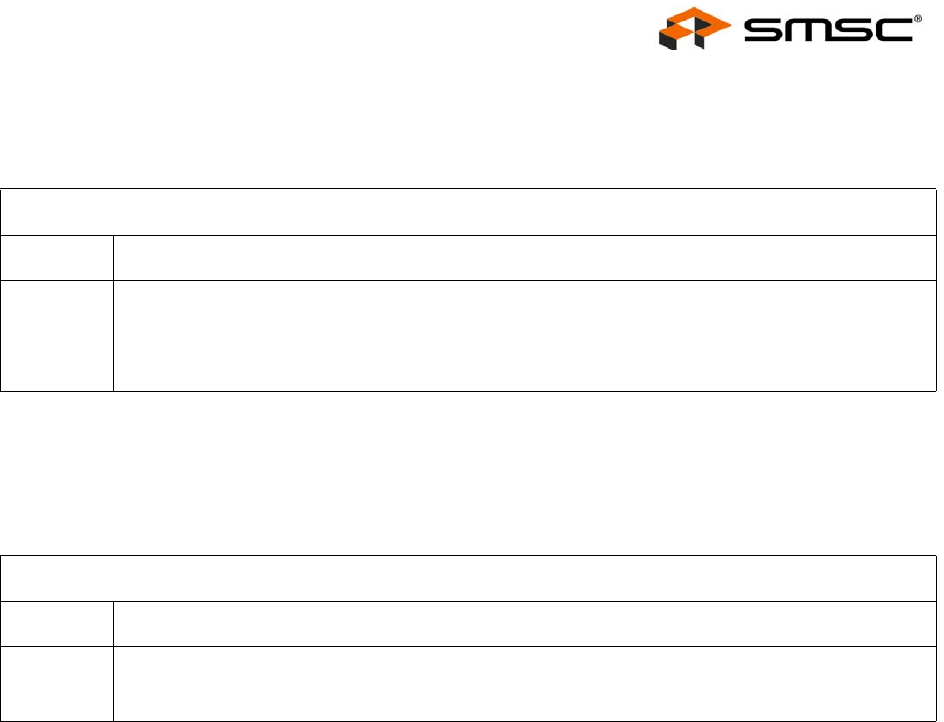

Table 9.5 Filter i Offset Bit Definitions

FILTER i OFFSET DESCRIPTION

FIELD DESCRIPTION

7:0 Pattern Offset: The offset of the first byte in the frame on which CRC is checked for wake-up frame

recognition. The minimum value of this field must be 12 since there should be no CRC check for

the destination address and the source address fields. The Host MAC checks the first offset byte

of the frame for CRC and checks to determine whether the frame is a wake-up frame. Offset 0 is

the first byte of the incoming frame's destination address.

Table 9.6 Filter i CRC-16 Bit Definitions

FILTER i CRC-16 DESCRIPTION

FIELD DESCRIPTION

15:0 Pattern CRC-16: This field contains the 16-bit CRC value from the pattern and the byte mask

programmed to the wake-up filter register function. This value is compared against the CRC

calculated on the incoming frame, and a match indicates the reception of a wakeup frame.