Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 29 Revision 1.4 (08-19-08)

DATASHEET

Note 3.1 The pin names for the twisted pair pins apply to a normal connection. If HP Auto-MDIX is

enabled and a reverse connection is detected or manually selected, the RX and TX pins

will be swapped internally.

Note 3.2 The pin names for the twisted pair pins apply to a normal connection. If HP Auto-MDIX is

enabled and a reverse connection is detected or manually selected, the RX and TX pins

will be swapped internally.

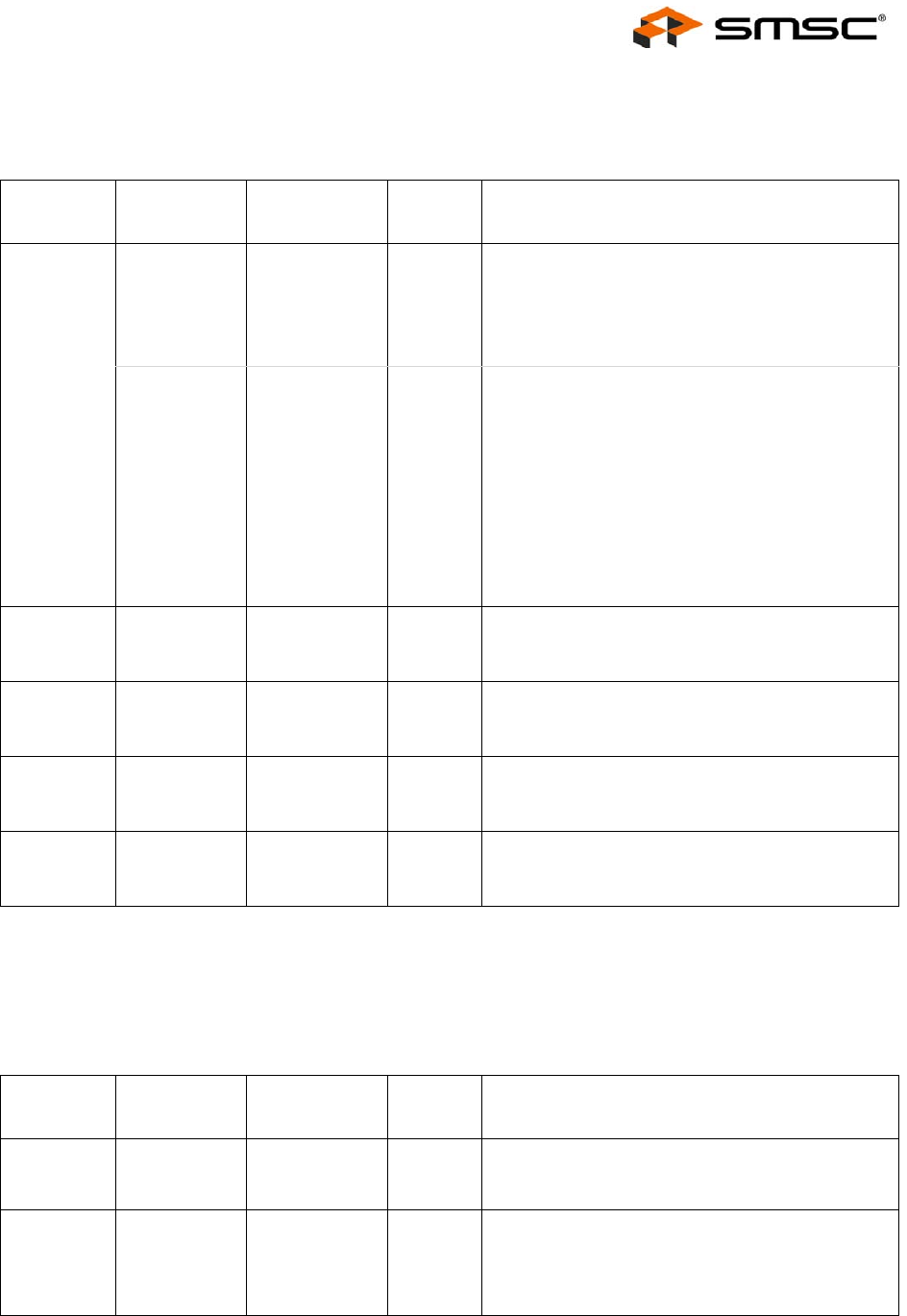

Table 3.2 LAN Port 2 Pins

PIN NAME SYMBOL

BUFFER

TYPE DESCRIPTION

83-86

Port 2 LED

Indicators

nP2LED[3:0] OD12 LED indicators: When configured as LED outputs

via the LED Configuration Register (LED_CFG),

these pins are open-drain, active low outputs and

the pull-ups and input buffers are disabled. The

functionality of each pin is determined via the

LED_CFG[9:8] bits.

General

Purpose I/O

Data

GPIO[7:4] IS/O12/

OD12

(PU)

General Purpose I/O Data: When configured as

GPIO via the LED Configuration Register

(LED_CFG), these general purpose signals are

fully programmable as either push-pull outputs,

open-drain outputs or Schmitt-triggered inputs by

writing the General Purpose I/O Configuration

Register (GPIO_CFG) and General Purpose I/O

Data & Direction Register (GPIO_DATA_DIR). The

pull-ups are enabled in GPIO mode. The input

buffers are disabled when set as an output.

Note: See Chapter 13, "GPIO/LED Controller,"

on page 163 for additional details.

127

Port 2

Ethernet TX

Negative

TXN2 AIO Ethernet TX Negative: Negative output of Port 2

Ethernet transmitter. See Note 3.2 for additional

information.

126

Port 2

Ethernet TX

Positive

TXP2 AIO Ethernet TX Positive: Positive output of Port 2

Ethernet transmitter. See Note 3.2 for additional

information.

124

Port 2

Ethernet RX

Negative

RXN2 AIO Ethernet RX Negative: Negative input of Port 2

Ethernet receiver. See Note 3.2 for additional

information.

123

Port 2

Ethernet RX

Positive

RXP2 AIO Ethernet RX Positive: Positive input of Port 2

Ethernet receiver. See Note 3.2 for additional

information.

Table 3.3 LAN Port 1 & 2 Power and Common Pins

PIN NAME SYMBOL

BUFFER

TYPE DESCRIPTION

119

Bias

Reference

EXRES AI Bias Reference: Used for internal bias circuits.

Connect to an external 12.4K ohm, 1% resistor to

ground.

114,117

+3.3V Port 1

Analog Power

Supply

VDD33A1 P +3.3V Port 1 Analog Power Supply

Refer to the LAN9311/LAN9311i application note

for additional connection information.