Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 141 Revision 1.4 (08-19-08)

DATASHEET

controller drives all the address bits as requested regardless of the actual size of the EEPROM. The

supported size ranges for I

2

C operation are shown in Table 10.2.

Note 10.1 Bits in the control byte are used as the upper address bits.

The I

2

C master interface runs at the standard-mode rate of 100KHz and is fully compliant with the

Philips

I

2

C-Bus Specification. Refer to the he Philips I

2

C-Bus Specification for detailed timing

information.

10.2.2.1 I

2

C Protocol Overview

I

2

C is a bi-directional 2-wire data protocol. A device that sends data is defined as a transmitter and a

device that receives data is defined as a receiver. The bus is controlled by a master which generates

the EE_SCL clock, controls bus access, and generates the start and stop conditions. Either the master

or slave may operate as a transmitter or receiver as determined by the master.

The following bus states exist:

Idle: Both EE_SDA and EE_SCL are high when the bus is idle.

Start & Stop Conditions: A start condition is defined as a high to low transition on the EE_ SDA

line while EE_ SCL is high. A stop condition is defined as a low to high transition on the EE_SDA

line while EE_SCL is high. The bus is considered to be busy following a start condition and is

considered free 4.7uS/1.3uS (for 100KHz and 400KHz operation, respectively) following a stop

condition. The bus stays busy following a repeated start condition (instead of a stop condition).

Starts and repeated starts are otherwise functionally equivalent.

Data Valid: Data is valid, following the start condition, when EE_SDA is stable while EE_SCL is

high. Data can only be changed while the clock is low. There is one valid bit per clock pulse. Every

byte must be 8 bits long and is transmitted msb first.

Acknowledge: Each byte of data is followed by an acknowledge bit. The master generates a ninth

clock pulse for the acknowledge bit. The transmitter releases EE_SDA (high). The receiver drives

EE_SDA low so that it remains valid during the high period of the clock, taking into account the

setup and hold times. The receiver may be the master or the slave depending on the direction of

the data. Typically the receiver acknowledges each byte. If the master is the receiver, it does not

generate an acknowledge on the last byte of a transfer. This informs the slave to not drive the next

byte of data so that the master may generate a stop or repeated start condition.

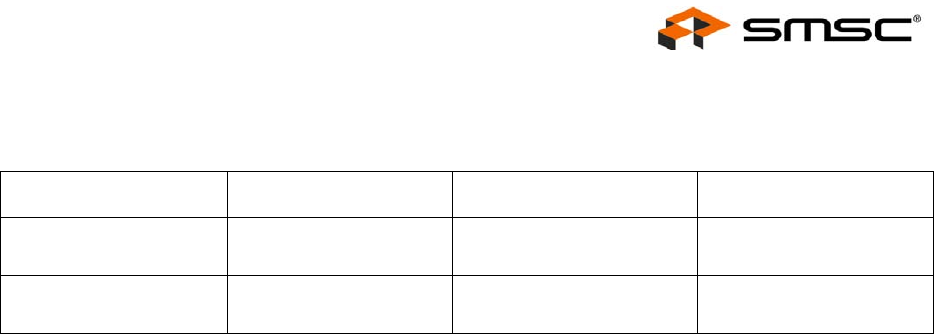

Table 10.2 I

2

C EEPROM Size Ranges

eeprom_size_strap[0] # OF ADDRESS BYTES EEPROM SIZE EEPROM TYPES

01 (Note 10.1) 16 x 8 through 2048 x 8 24xx00, 24xx01, 24xx02,

24xx04, 24xx08, 24xx16

1 2 4096 x 8 through 65536 x 8 24xx32, 24xx64, 24xx128,

24xx256, 24xx512