Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 281 Revision 1.4 (08-19-08)

DATASHEET

14.3.8 Host MAC Flow Control Register (HMAC_FLOW)

This read/write register controls the generation and reception of the Control (Pause command) frames

by the Host MAC’s flow control block. The control frame fields are selected as specified in the 802.3

Specification and the Pause-Time value from this register is used in the “Pause Time” field of the

control frame. In full-duplex mode the FCBSY bit is set until the control frame is completely transferred.

In half-duplex mode FCBSY is set while back pressure is being asserted. The host has to make sure

that the FCBSY bit is cleared before writing the register. The Pass Control Frame bit (FCPASS) does

not affect the sending of the frames, including Control Frames, to the host. The Flow Control Enable

(FCEN) bit enables the receive portion of the Flow Control block.

This register is used in conjunction with the Host MAC Automatic Flow Control Configuration Register

(AFC_CFG) in the System CSR’s to configure flow control. Software flow control is initiated using the

AFC_CFG register.

Note: The Host MAC will not transmit pause frames or assert back pressure if the transmitter is

disabled.

Note: For the Host MAC, flow control/backpressure is to/from the switch fabric, not the external

network.

Offset: 8h Size: 32 bits

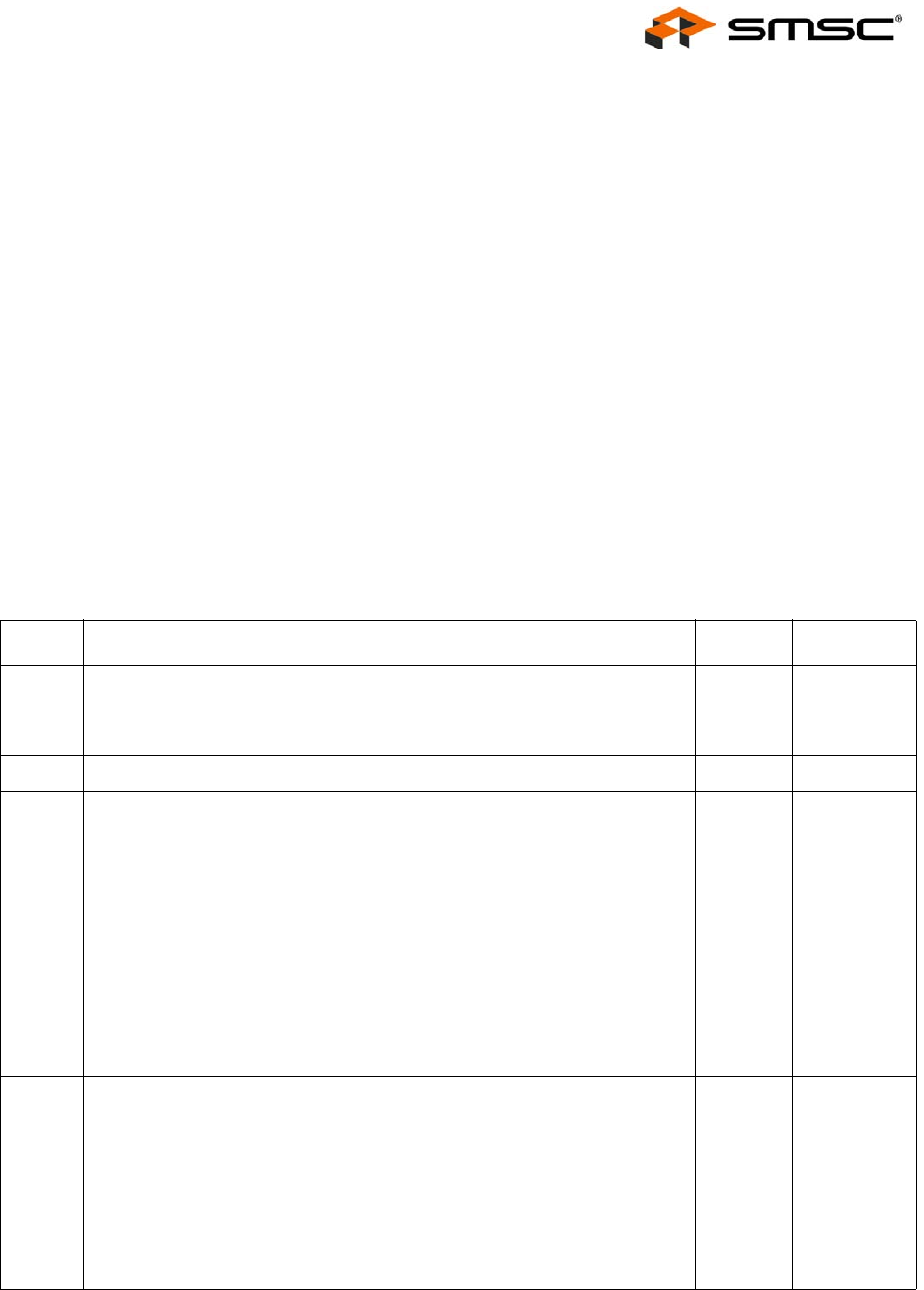

BITS DESCRIPTION TYPE DEFAULT

31:16 Pause Time (FCPT)

This field indicates the value to be used in the PAUSE TIME field in the

control frame. This field must be initialized before full-duplex automatic flow

control is enabled.

R/W 0000h

15:3

RESERVED RO -

2

Pass Control Frames (FCPASS)

When set, the Host MAC sets the packet filter bit in the receive packet status

to indicate to the application that a valid pause frame has been received.

The application must accept or discard a received frame based on the

packet filter control bit. The Host MAC receives, decodes and performs the

Pause function when a valid Pause frame is received in Full-Duplex mode

and when flow control is enabled (FCE bit set). When this bit is cleared, the

Host MAC resets the Packet Filter bit in the Receive packet status.

The Host MAC always passes the data of all frames it receives (including

flow control frames) to the application. Frames that do not pass address

filtering, as well as frames with errors, are passed to the application. The

application must discard or retain the received frame’s data based on the

received frame’s STATUS field. Filtering modes (promiscuous mode, for

example) take precedence over the FCPASS bit.

R/W 0b

1

Flow Control Enable (FCEN)

When set, enables the Host MAC flow control function. The Host MAC

decodes all incoming frames for control frames; if it receives a valid control

frame (PAUSE command), it disables the transmitter for a specified time

(Decoded pause time x slot time). When this bit is cleared, the Host MAC

flow control function is disabled; the MAC does not decode frames for

control frames.

Note: Flow Control is applicable when the Host MAC is set in full duplex

mode. In half-duplex mode, this bit enables the backpressure

function to control the flow of received frames to the Host MAC.

R/W 0b