Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 370 SMSC LAN9311/LAN9311i

DATASHEET

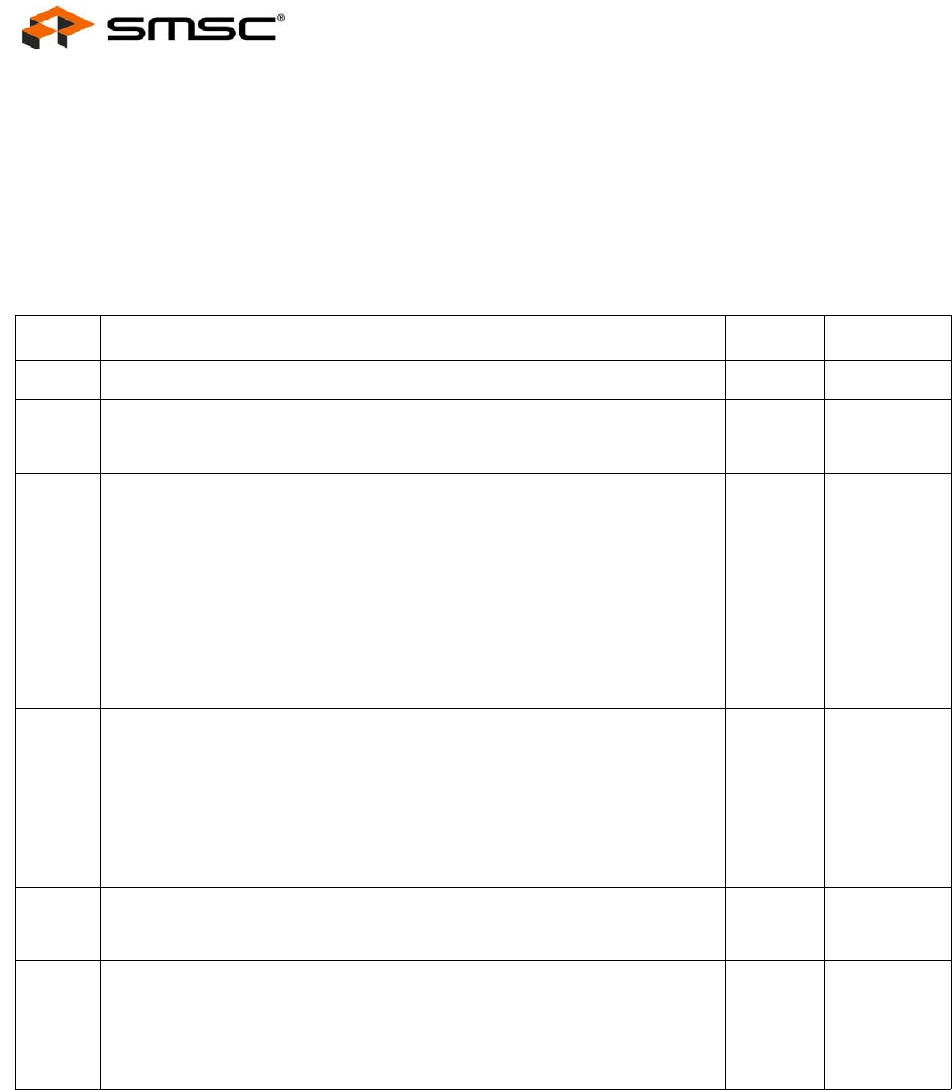

14.5.3.3 Switch Engine ALR Write Data 1 Register (SWE_ALR_WR_DAT_1)

This register is used in conjunction with the Switch Engine ALR Write Data 0 Register

(SWE_ALR_WR_DAT_0) and contains the last 32 bits of ALR data to be manually written via the Make

Entry command in the Switch Engine ALR Command Register (SWE_ALR_CMD).

Register #: 1802h Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:25 RESERVED RO -

24

Valid

When set, this bit makes the entry valid. It can be cleared to invalidate a

previous entry that contained the specified MAC address.

R/W 0b

23

Age/Override

This bit is used by the aging and forwarding processes.

If the Static bit of this register is cleared, this bit should be set so that the

entry will age in the normal amount of time.

If the Static bit is set, this bit is used as a port state override bit. When set,

packets received with a destination address that matches the MAC address

in the SWE_ALR_WR_DAT_1 and SWE_ALR_WR_DAT_0 registers will be

forwarded regardless of the port state of the ingress or egress port(s). This

is typically used to allow the reception of BPDU packets in the non-

forwarding state.

R/W 0b

22

Static

When this bit is set, this entry will not be removed by the aging process

and/or be changed by the learning process. When this bit is cleared, this

entry will be automatically removed after 5 to 10 minutes of inactivity.

Inactivity is defined as no packets being received with a source address that

matches this MAC address.

Note: This bit is normally set when adding manual entries. It must be

cleared when removing an entry (clearing the Valid bit).

R/W 0b

21

Filter

When set, packets with a destination address that matches this MAC

address will be filtered.

R/W 0b

20:19

Priority

These bits specify the priority that is used for packets with a destination

address that matches this MAC address. This priority is only used if the

Static bit of this register is set, and the DA Highest Priority (bit 5) in the

Switch Engine Global Ingress Configuration Register

(SWE_GLOBAL_INGRSS_CFG) is set.

R/W 00b