Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i 295 Revision 1.4 (08-19-08)

DATASHEET

14.4.2.5 Port x PHY Auto-Negotiation Advertisement Register (PHY_AN_ADV_x)

This read/write register contains the advertised ability of the Port x PHY and is used in the Auto-

Negotiation process with the link partner.

Note: This register is re-written by the EEPROM Loader following the release of reset or a RELOAD

command. Refer to Section 10.2.4, "EEPROM Loader," on page 150 for additional information.

Index (decimal): 4 Size: 16 bits

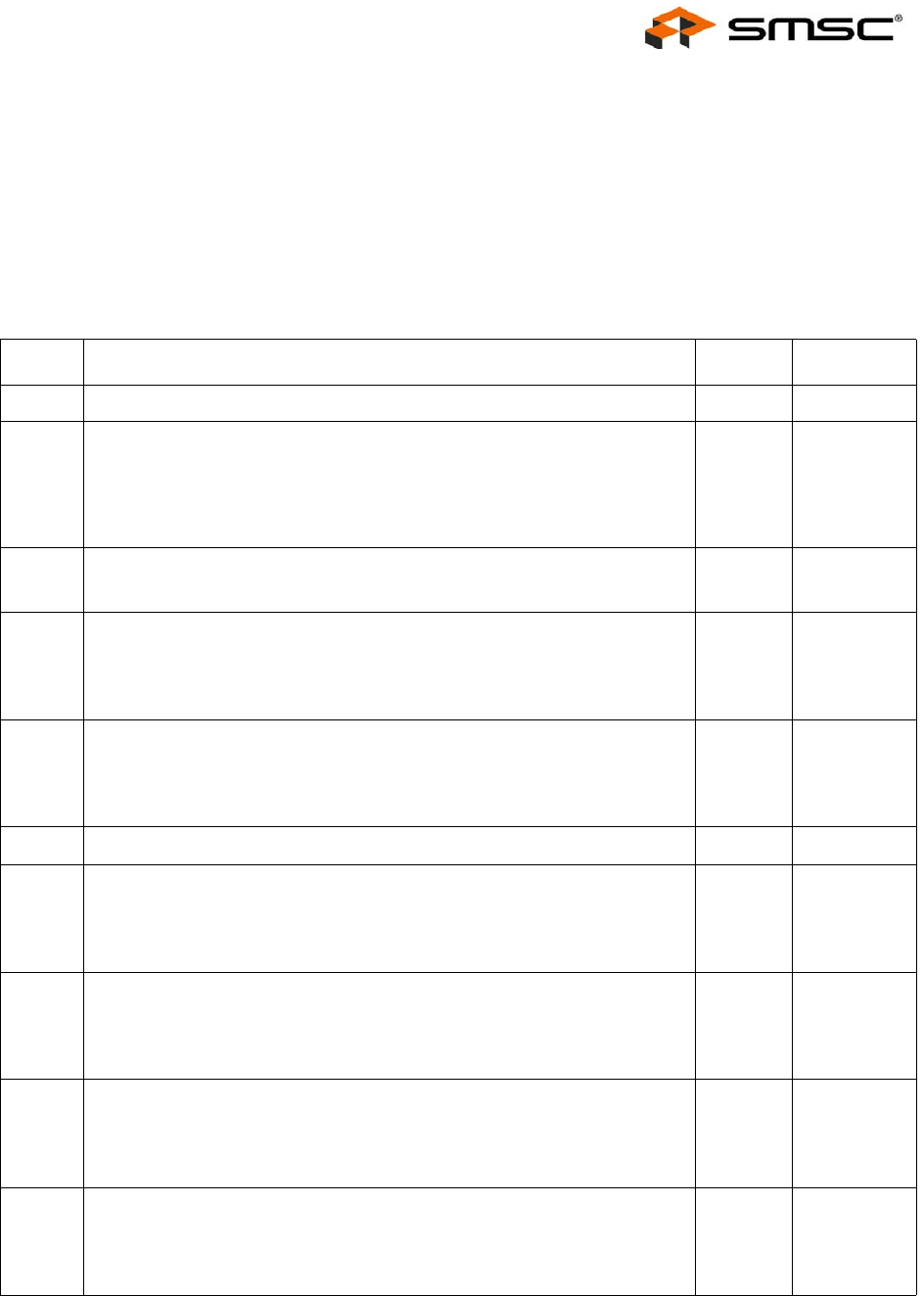

BITS DESCRIPTION TYPE DEFAULT

15:14 RESERVED RO -

13

Remote Fault

This bit determines if remote fault indication will be advertised to the link

partner.

0: Remote fault indication not advertised

1: Remote fault indication advertised

R/W 0b

12

RESERVED

Note:

This bit should be written as 0.

R/W 0b

11

Asymmetric Pause

This bit determines the advertised asymmetric pause capability.

0: No Asymmetric PAUSE toward link partner advertised

1: Asymmetric PAUSE toward link partner advertised

R/W 0b

Note 14.53

10

Symmetric Pause

This bit determines the advertised symmetric pause capability.

0: No Symmetric PAUSE toward link partner advertised

1: Symmetric PAUSE toward link partner advertised

R/W Note 14.53

Note 14.54

9

RESERVED RO -

8

100BASE-X Full Duplex

This bit determines the advertised 100BASE-X full duplex capability.

0: 100BASE-X full duplex ability not advertised

1: 100BASE-X full duplex ability advertised

R/W 1b

7

100BASE-X Half Duplex

This bit determines the advertised 100BASE-X half duplex capability.

0: 100BASE-X half duplex ability not advertised

1: 100BASE-X half duplex ability advertised

R/W 1b

6

10BASE-T Full Duplex

This bit determines the advertised 10BASE-T full duplex capability.

0: 10BASE-T full duplex ability not advertised

1: 10BASE-T full duplex ability advertised

R/W Note 14.55

Table 14.8

5

10BASE-T Half Duplex

This bit determines the advertised 10BASE-T half duplex capability.

0: 10BASE-T half duplex ability not advertised

1: 10BASE-T half duplex ability advertised

R/W Note 14.56

Table 14.9