Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08) 118 SMSC LAN9311/LAN9311i

DATASHEET

The Filter i Byte Mask defines which incoming frame bytes Filter i will examine to determine whether

or not this is a wake-up frame. Table 9.3, describes the byte mask’s bit fields.

The Filter i command register controls Filter i operation. Table 9.4 shows the Filter i command register.

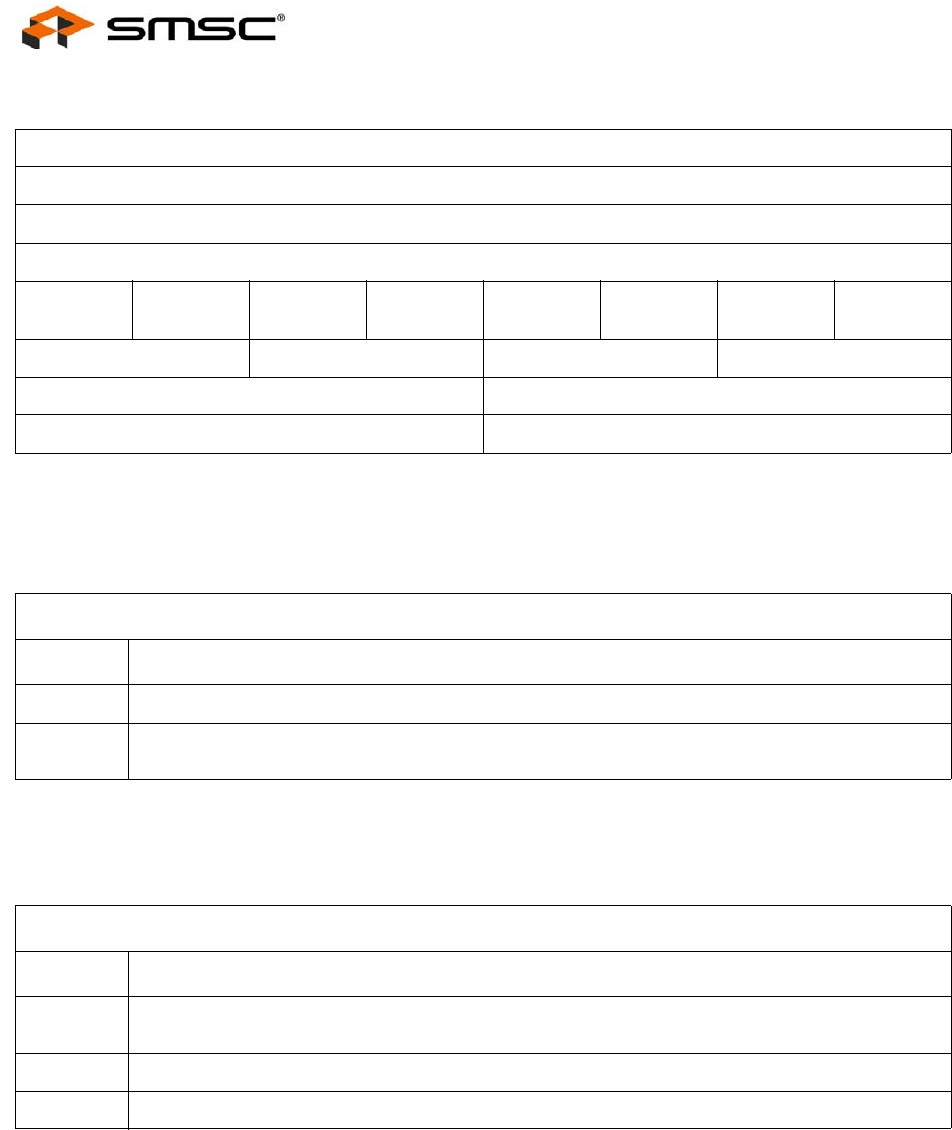

Table 9.2 Wake-Up Frame Filter Register Structure

Filter 0 Byte Mask

Filter 1 Byte Mask

Filter 2 Byte Mask

Filter 3 Byte Mask

Reserved Filter 3

Command

Reserved Filter 2

Command

Reserved Filter 1

Command

Reserved Filter 0

Command

Filter 3 Offset Filter 2 Offset Filter 1Offset Filter 0 Offset

Filter 1 CRC-16 Filter 0 CRC-16

Filter 3 CRC-16 Filter 2 CRC-16

Table 9.3 Filter i Byte Mask Bit Definitions

FILTER I BYTE MASK DESCRIPTION

FIELD DESCRIPTION

31 Must be zero (0)

30:0

Byte Mask: If bit j of the byte mask is set, the CRC machine processes byte number pattern - (offset

+ j) of the incoming frame. Otherwise, byte pattern - (offset + j) is ignored.

Table 9.4 Filter i Command Bit Definitions

FILTER i COMMANDS

FIELD DESCRIPTION

3 Address Type: Defines the destination address type of the pattern. When bit is set, the pattern

applies only to multicast frames. When bit is cleared, the pattern applies only to unicast frames.

2:1

RESERVED

0 Enable Filter: When bit is set, Filter i is enabled, otherwise, Filter i is disabled.