AMD Geode™ SC3200 Processor Data Book 147

Core Logic Module

32581C

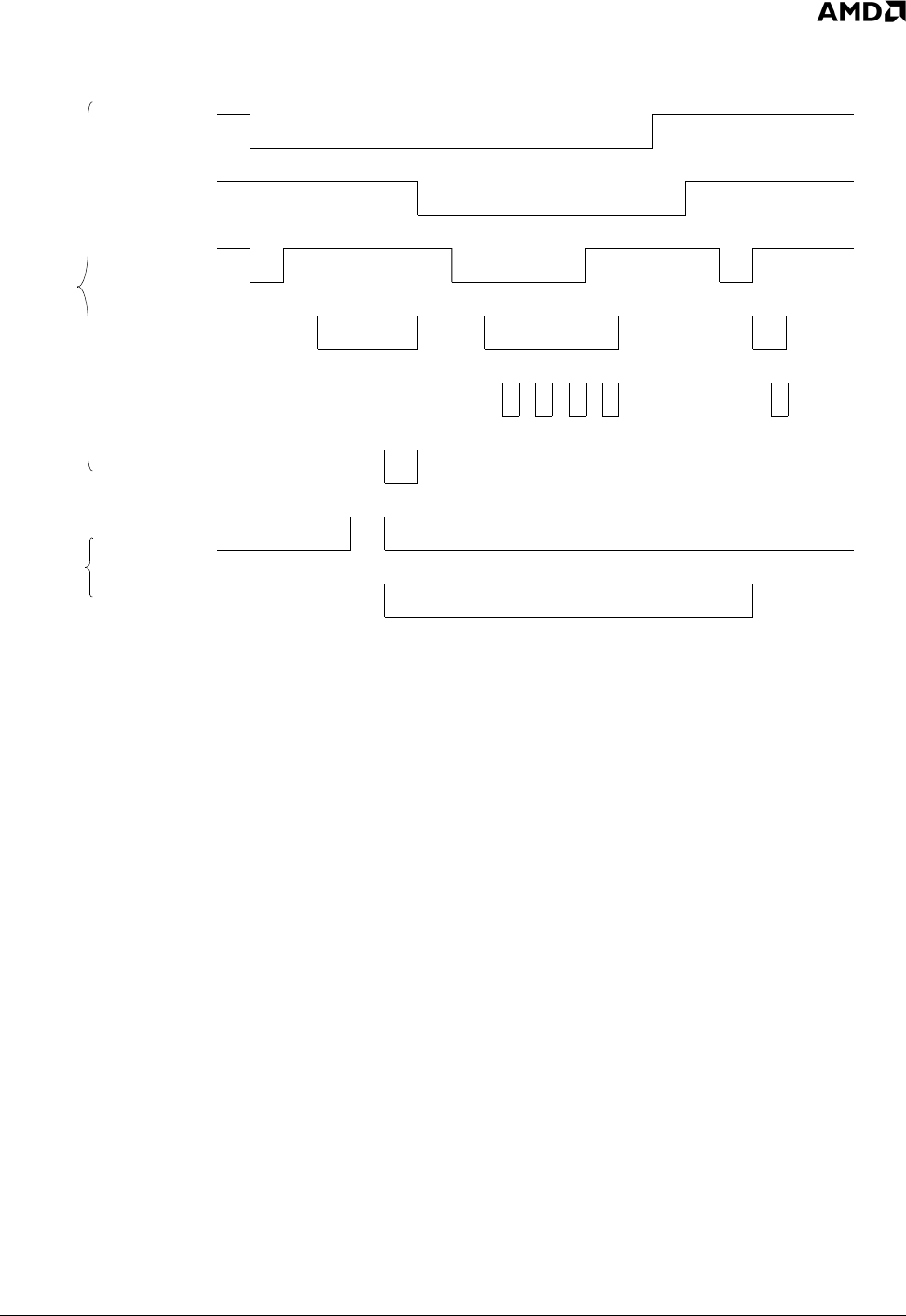

Figure 6-3. PCI to ISA Cycles with Delayed Transaction Enabled

6.2.5.3 Sub-ISA Bus Data Steering

The Core Logic module performs all of the required data

steering from SD[7:0] to SD[15:0] during normal 8-bit ISA

cycles, as well as during DMA and ISA master cycles. It

handles data transfers between the 32-bit PCI data bus

and the ISA bus. 8/16-bit devices can reside on the ISA

bus. Various PC-compatible I/O registers, DMA controller

registers, interrupt controller registers, and counter/timer

registers lie on the on-chip I/O data bus. Either the PCI bus

master or the DMA controllers can become the bus owner.

When the PCI bus master is the bus owner, the Core Logic

module data steering logic provides data conversion nec-

essary for 8/16/32-bit transfers to and from 8/16-bit devices

on either the Sub-ISA bus or the 8-bit registers on the on-

chip I/O data bus. When PCI data bus drivers of the Core

Logic module are in TRI-STATE, data transfers between

the PCI bus master and PCI bus devices are handled

directly via the PCI data bus.

When the DMA requestor is the bus owner, the Core Logic

module allows 8/16-bit data transfer between the Sub-ISA

bus and the PCI data bus.

6.2.5.4 I/O Recovery Delays

In normal operation, the Core Logic module inserts a delay

between back-to-back ISA I/O cycles that originate on the

PCI bus. The default delay is four ISACLK cycles. Thus, the

second of consecutive I/O cycles is held in the ISA bus

controller until this delay count has expired. The delay is

measured between the rising edge of IOR#/IOW# and the

falling edge of BALE. This delay can be adjusted to a

greater delay through the ISA I/O Recovery Control register

(F0 Index 51h).

Note: This delay is not inserted for a 16-bit Sub-ISA I/O

access that is split into two 8-bit I/O accesses.

REQ#

GNT#

FRAME#

IRDY#

TRDY#

STOP#

RD#, IOR#

BALE

Fast-PCI

1

1

1

1

1 - GX1 transaction

2

3

2 - IDE bus master - starts and completes

3 - End of ISA cycle

ISA