332 AMD Geode™ SC3200 Processor Data Book

Video Processor Module - Video Processor Registers - Function 4

32581C

7.3.2.1 Video Processor Support Registers - F4BAR0

F4 Index 10h, Base Address Register 0 (F4BAR0) sets the

base address that allows PCI access to the Video Proces-

sor support registers, not including VIP. A separate base

address register (F4BAR2) is used to access VIP support

registers (see Section 7.3.2.2 on page 345).

Note: Reserved bits that are not defined as “must be set

to 0 or 1" should be written with a value that is read

from them.

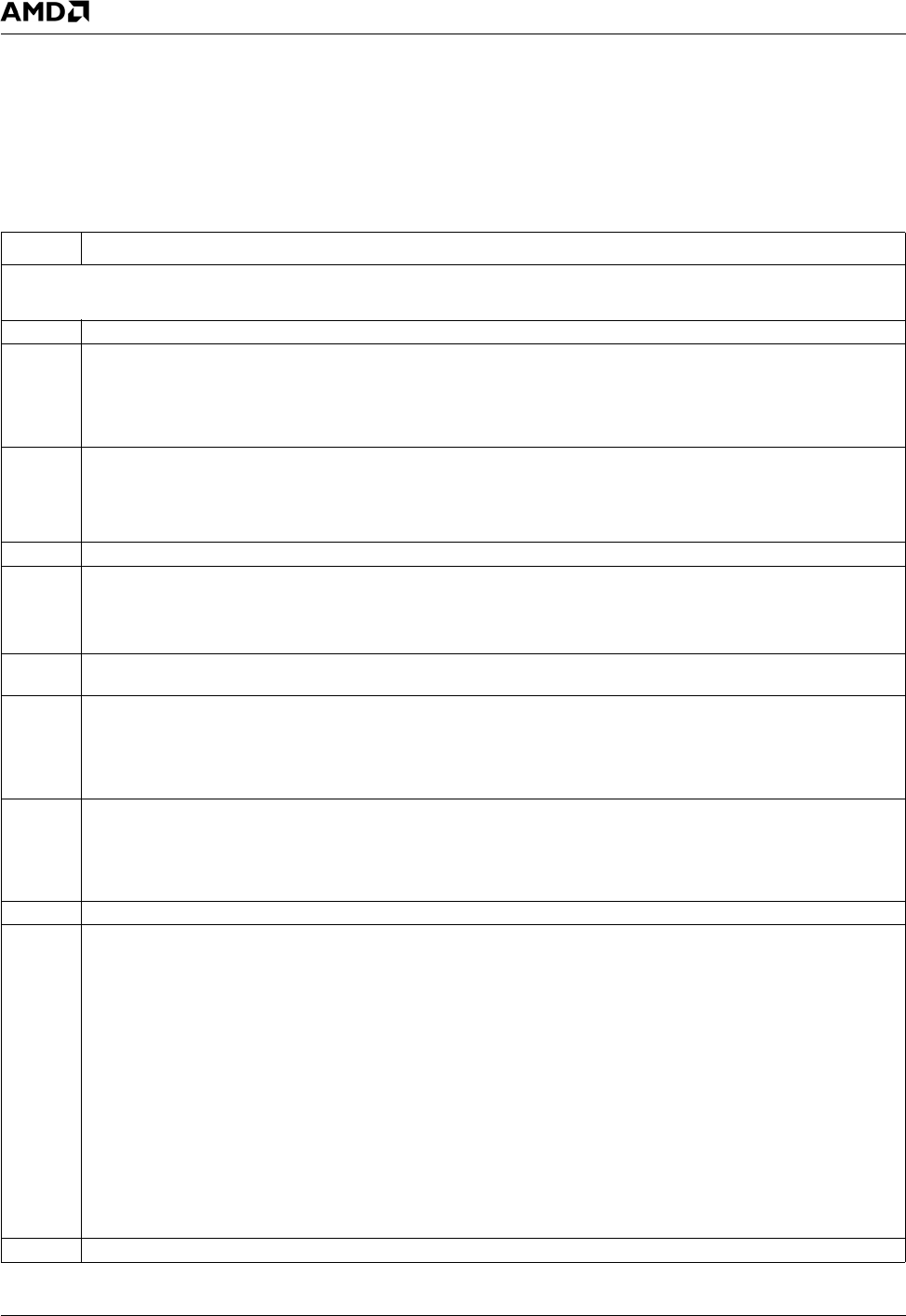

Table 7-7. F4BAR0+Memory Offset: Video Processor Configuration Registers

Bit Description

Offset 00h-03h Video Configuration Register (R/W) Reset Value: 00000000h

Configuration register for options of the motion video acceleration hardware.

31:29 Reserved. Must be set to 0.

28 EN_42X (Enable 4:2:x Format). Allows format selection.

0: 4:2:2 format.

1: 4:2:0 format.

Note: When input video stream is RGB (i.e., F4BAR0+Memory Offset 4Ch[13] = 1), this bit must be set to 0.

27 BIT_8_LINE_SIZE. When enabled, this bit increases line size from VID_LIN_SIZ (bits [15:8]) DWORDs by adding 256

DWORDs.

0: Disable.

1: Enable.

26:25 Reserved. Must be set to 0.

24:16 INIT_RD_ADDR (Initial Buffer Read Address). This field preloads the starting read address for the line buffers at the

beginning of each display line. It is used for hardware clipping of the video window at the left edge of the active display. It

represents the DWORD address of the source pixel which is to be displayed first.

For an unclipped window, this value should be 0. For 4:2:0 format, set bits [17:16] to 00.

15:8 VID_LIN_SIZ (Video Line Size). Represents the number of DWORDs that make up the horizontal size of the source video

data.

7 YFILT_EN (Y Filter Enable). Enables/disables the vertical filter.

0: Disable. Upscaling done by repeating pixels.

1: Enable. Upscaling done by interpolating pixels.

Note: This bit is used with Y upscaling logic. Reset to 0 when not required.

6 XFILT_EN (X Filter Enable). Enables/disables the horizontal filter.

0: Disable. Upscaling done by repeating pixels.

1: Enable. Upscaling done by interpolating pixels.

Note: This bit is used with X upscaling logic. Reset to 0 when not required.

5:4 Reserved.

3:2 VID_FMT (Video Format). Byte ordering of video data on the Video Input bus (VPD[7:0]). The interpretation of these bits

depends on the settings of bit 13 (GV_SEL) in the Video De-Interlacing and Alpha Control register (F4BAR0+Memory Offset

4Ch) and bit 28 (EN_42X) of this register.

If GV_SEL = 0 and EN_42X = 0:

00: Cb Y0 Cr Y1 10: Y0 Cb Y1 Cr

01: Y1 Cr Y0 Cb 11: Y0 Cr Y1 Cb

If GV_SEL = 0 and EN_42X = 1:

00: Y0 Y1 Y2 Y3 10: Y1 Y0 Y3 Y2

01: Y3 Y2 Y1 Y0 11: Y1 Y2 Y3 Y0

If GV_SEL = 1 and EN_42X = 0:

00: P1L P1M P2L P2M 10: P1M P1L P2M P2L

01: P2M P2L P1M P1L 11: P1M P2L P2M P1L

If GV_SEL = 1 and EN_42X = 1: Reserved

Note: Both RGB 5:6:5 and YUV 4:2:2 contain two pixels in each 32-bit DWORD. YUV 4:2:0 contains a stream of Y data

for each line, followed by U and V data for that same line.

1 Reserved.