AMD Geode™ SC3200 Processor Data Book 337

Video Processor Module - Video Processor Registers - Function 4

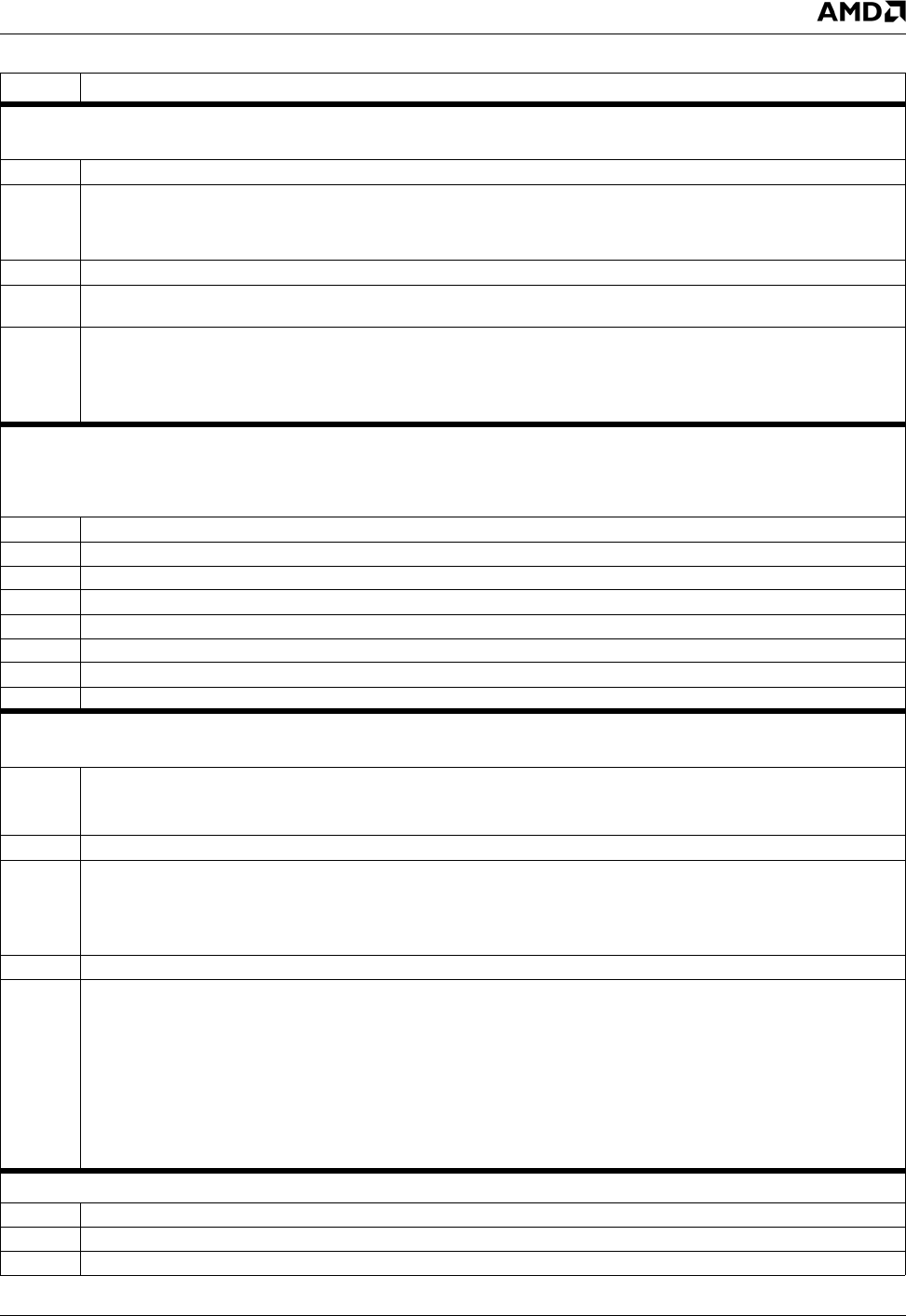

32581C

Offset 3Ch-3Fh Video Downscaler Control Register (R/W) Reset Value: 00000000h

Controls the characteristics of the integrated video downscaler.

31:7 Reserved

6 DTS (Downscale Type Select).

0: Type A (Downscale formula is 1/m+1, m pixels are dropped, 1 pixel is kept).

1: Type B (Downscale formula is m/m+1, m pixels are kept, 1 pixel is dropped).

5 Reserved.

4:1 DFS (Downscale Factor Select). Determines the downscale factor to be programmed into these bits, where m is used to

derive the desired downscale factor depending on bit 6 (DTS).

0 DCF (Downscaler and Filtering). Enables/disables downscaler and filtering logic.

0: Disable.

1: Enable.

Note: No downscaling support for RGB 5:6:5 and YUV 4:2:0 video formats.

Offset 40h-43h Video Downscaler Coefficient Register (R/W) Reset Value: 00000000h

Indicates filter coefficients. The filters can be programmed independently to increase video quality when the downscaler is implemented.

Valid values for each filter coefficient are 0-15. The sum of coefficients must be 16. FLT_CO_4 is used with the earliest pixels and

FLT_CO_1 is used with the latest. Only luminance values of pixels are filtered.

31:28 Reserved

27:24 FLT_CO_4 (Filter Coefficient 4). For the tap-4 filter.

23:20 Reserved

19:16 FLT_CO_3 (Filter Coefficient 3). For the tap-3 filter.

15:12 Reserved

11:8 FLT_CO_2 (Filter Coefficient 2). For the tap-2 filter.

7:4 Reserved

3:0 FLT_CO_1 (Filter Coefficient 1). For the tap-1 filter.

Offset 44h-47h CRC Signature Register (R/W) Reset Value: xxxxx100h

Signature values stored in this register can be read by the host. This register is used for test purposes.

31:8 SIG_VALUE (Signature Value). (Read Only) A 24-bit signature value is stored in this bit field and can be read at any time.

The signature is produced from the RGB data output of the mixer. This bit field is used for test purpose only.

See SIGN_EN (bit 0) description for more information.

7:3 Reserved

2 SIGN_FREE (Signature Free Run).

0: Disable. (Default) If this bit was previously set to 1, the signature process stops at the end of the current frame (i.e., at

the next falling edge of VSYNC).

1: Enable. If SIGN_EN (bit 0) = 1, the signature register captures data continuously across multiple frames.

1 Reserved.

0 SIGN_EN (Signature Enable).

0: Disable. (Default) The SIG_VALUE (bits [31:8]) is reset to 000001h and held (no capture).

1: Enable. The next falling edge of VSYNC is counted as the start of the frame to be used for CRC checking with each pixel

clock beginning with the next VSYNC.

If SIGN_FREE (bit 2) = 1, the signature register captures the pixel data signature continuously across multiple frames.

If SIGN_FREE (bit 2) = 0, a signature is captured for one frame at a time, starting from the next falling VSYNC.

After a signature capture, the SIG_VALUE can be read to determine the CRC check status. SIGN_EN can then be reset to

initialize the SIG_VALUE as an essential preparation for the next round of CRC check.

Offset 48h-4Bh Device and Revision Identification (RO) Reset Value: 0000xxxxh

31:16 Reserved.

15:8 REV_ID (Revision ID).

See the AMD Geode™ SC3200 Specification Update document for value.

7:0 DEV_ID (Device ID). See the AMD Geode™ SC3200 Specification Update document for value.

Table 7-7. F4BAR0+Memory Offset: Video Processor Configuration Registers (Continued)

Bit Description