AMD Geode™ SC3200 Processor Data Book 349

8

Debugging and Monitoring 32581C

8.0Debugging and Monitoring

8.1 Testability (JTAG)

The Test Access Port (TAP) allows board level interconnec-

tion verification and chip production tests. An IEEE-

1149.1a compliant test interface, TAP supports all IEEE

mandatory instructions as well as several optional instruc-

tions for added functionality. See Table 8-1 • for a summary

of all instructions support. For further information on JTAG,

refer to IEEE Standard 1149.1a-1993 Test Access Port and

Boundary-Scan Architecture.

8.1.1 Mandatory Instruction Support

The TAP supports all IEEE mandatory instructions, includ-

ing:

• BYPASS.

Presents the shortest path through a given chip (a 1-bit

shift register).

• EXTEST

Drives data loaded into the JTAG path (possibly with a

SAMPLE/PRELOAD instruction) to output pins.

• SAMPLE/PRELOAD

Captures chip inputs and outputs.

8.1.2 Optional Instruction Support

The TAP supports the following IEEE optional instructions:

• IDCODE

Presents the contents of the Device Identification

register in serial format.

• CLAMP

Ensures that the Bypass register is connected between

TDI and TDO, and then drives data that was loaded into

the Boundary Scan register (e.g., via SAMPLE-

PRELOAD instruction) to output signals. These signals

do not change while the CLAMP instruction is selected.

• HiZ

Puts all chip outputs in inactive (floating) state

(including all pins that do not require a TRI-STATE

output for normal functionality). Note that not all pull-up

resistors are disabled in this state.

8.1.3 JTAG Chain

Balls that are not part of the JTAG chain:

• USB I/Os

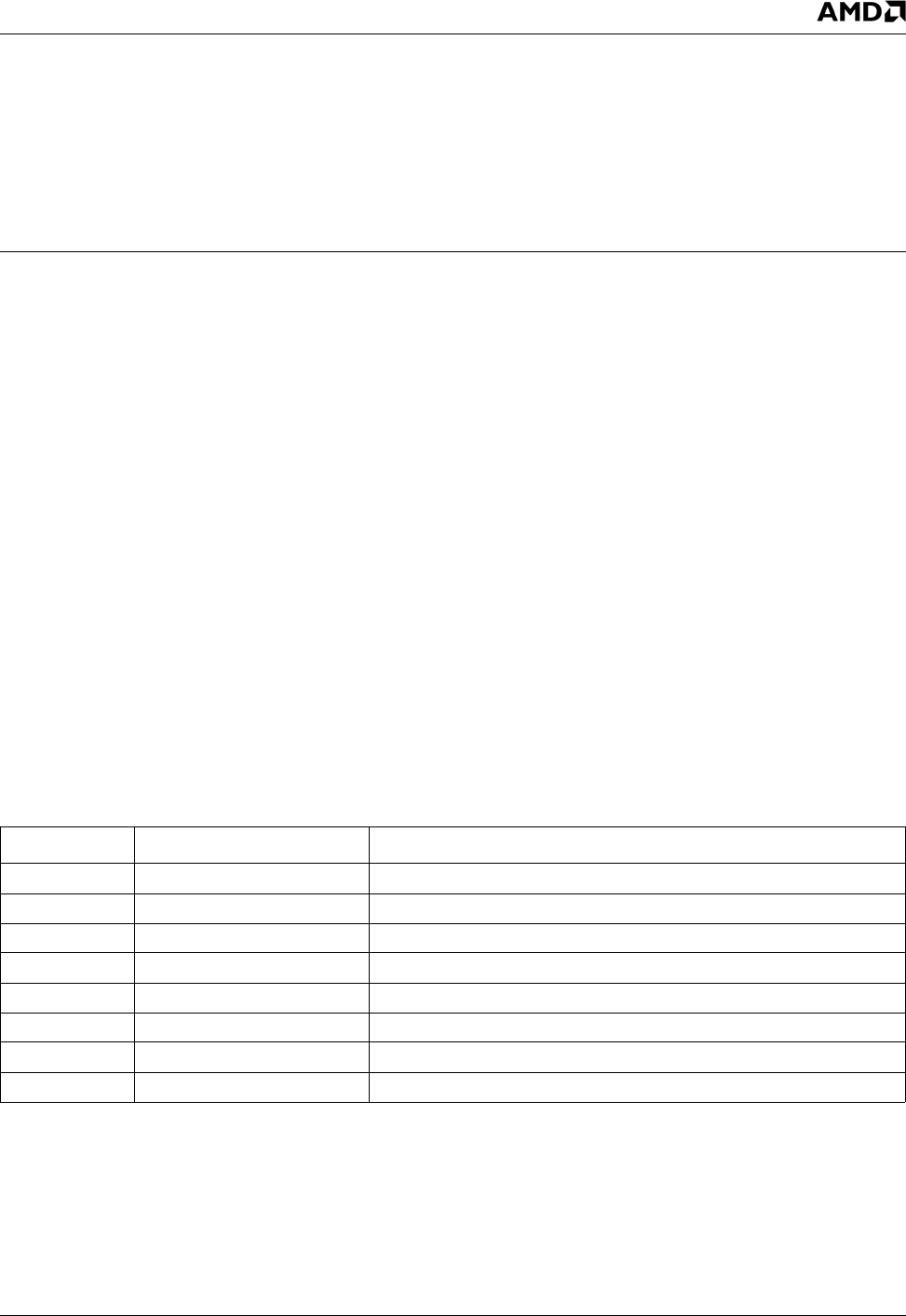

Table 8-1. JTAG Mode Instruction Support

Code Instruction Activity

000 EXTEST Drives shifted data to output pins.

001 SAMPLE/PRELOAD Captures inputs and system outputs.

010 IDCODE Scans out device identifier.

011 HIZ Puts all output and bidirectional pins in TRI-STATE.

100 CLAMP Drives fixed data from Boundary Scan register.

101 Reserved

110 Reserved

111 BYPASS Presents shortest external path through device.