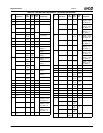

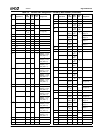

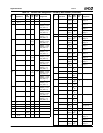

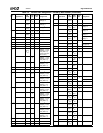

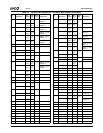

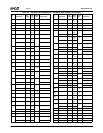

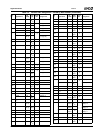

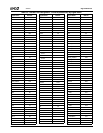

AMD Geode™ SC3200 Processor Data Book 33

Signal Definitions

32581C

F29 TDI I

(PU

22.5

)

IN

PCI

V

IO

---

F30 GTEST I

(PD

22.5

)

IN

T

V

IO

---

F31 VPCKIN I IN

T

V

IO

---

G1 STOP# I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

D15 I/O

(PU

22.5

)

IN

PCI

,

O

PCI

G2 V

SS

GND --- --- ---

G3 V

IO

PWR --- --- ---

G4 V

SS

GND --- --- ---

G28 V

SS

GND --- --- ---

G29 V

IO

PWR --- --- ---

G30 V

SS

GND --- --- ---

G31 VPD7 I IN

T

V

IO

---

H1 SERR# I/O

(PU

22.5

)

IN

PCI

,

OD

PCI

V

IO

---

H2 PERR# I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

---

H3 LOCK# I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

---

H4 C/BE3# I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

D11 I/O

(PU

22.5

)

IN

PCI

,

O

PCI

H28 VPD6 I IN

T

V

IO

---

H29 VPD5 I IN

T

V

IO

---

H30 VPD4 I IN

T

V

IO

---

H31 VPD3 I IN

T

V

IO

---

J1 AD13 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

A13 O O

PCI

J2 C/BE1# I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

D9 I/O

(PU

22.5

)

IN

PCI

,

O

PCI

J3 AD15 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

A15 O O

PCI

J4 PAR I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

D12 I/O

(PU

22.5

)

IN

PCI

,

O

PCI

J28 VPD2 I IN

T

V

IO

---

J29 VPD1 I IN

T

V

IO

---

J30 VPD0 I IN

T

V

IO

---

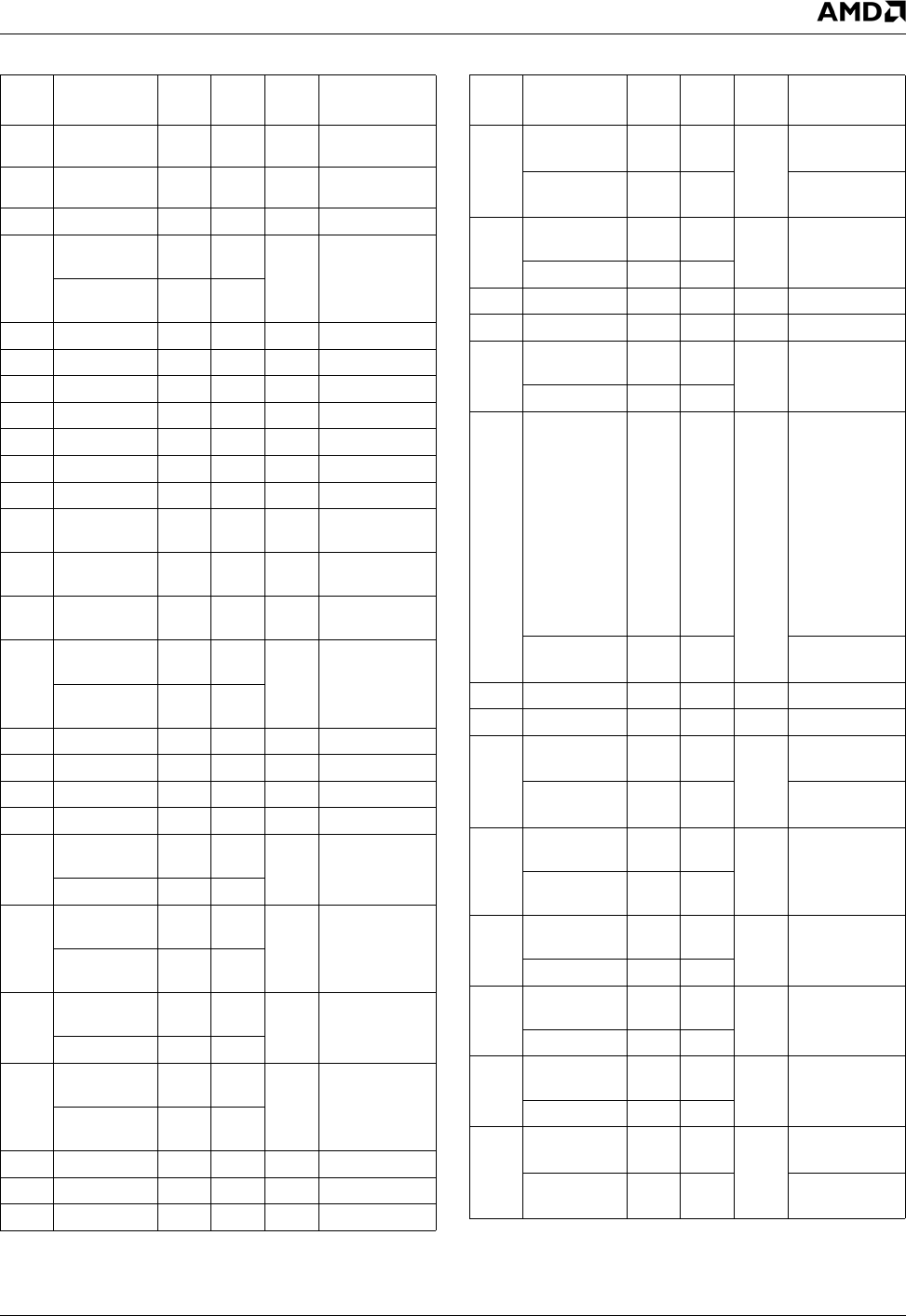

Ball

No. Signal Name

I/O

(PU/PD)

Buffer

1

Type

Power

Rail Configuration

J31 GPIO39 I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

PMR[14]

4

= 0 and

PMR[22]

4

= 0

SERIRQ I/O IN

PCI

,

O

PCI

PMR[14]

4

= 1 and

PMR[22]

4

= 1

K1 AD11 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

A11 O O

PCI

K2 V

IO

PWR --- --- ---

K3 V

SS

GND --- --- ---

K4 AD14 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

A14 O O

PCI

K28 GPIO38/IRRX2 I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

PMR[14]

4

= 0 and

PMR[22]

4

= 0. The

IRRX2 input is con-

nected to the input

path of GPIO38.

There is no logic

required to enable

IRRX2, just a sim-

ple connection.

Hence, when

GPIO38 is the

selected function,

IRRX2 is also

selected.

LPCPD# O O

PCI

PMR[14]

4

= 1 and

PMR[22]

4

= 1

K29 V

IO

PWR --- --- ---

K30 V

SS

GND --- --- ---

K31 GPIO37 I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

PMR[14]

4

= 0 and

PMR[22]

4

= 0

LFRAME# O O

PCI

PMR[14]

4

= 1 and

PMR[22]

4

= 1

L1 C/BE0# I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

D8 I/O

(PU

22.5

)

IN

PCI

,

O

PCI

L2 AD9 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

A9 O O

PCI

L3 AD10 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

A10 O O

PCI

L4 AD12 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

A12 O O

PCI

L28 GPIO36 I/O

(PU

22.5

)

IN

PCI

,

O

PCI

V

IO

PMR[14]

4

= 0 and

PMR[22]

4

= 0

LDRQ# I IN

PCI

PMR[14]

4

= 1 and

PMR[22]

4

= 1

Ball

No. Signal Name

I/O

(PU/PD)

Buffer

1

Type

Power

Rail Configuration

Table 3-2. BGU481 Ball Assignment - Sorted by Ball Number (Continued)