336 AMD Geode™ SC3200 Processor Data Book

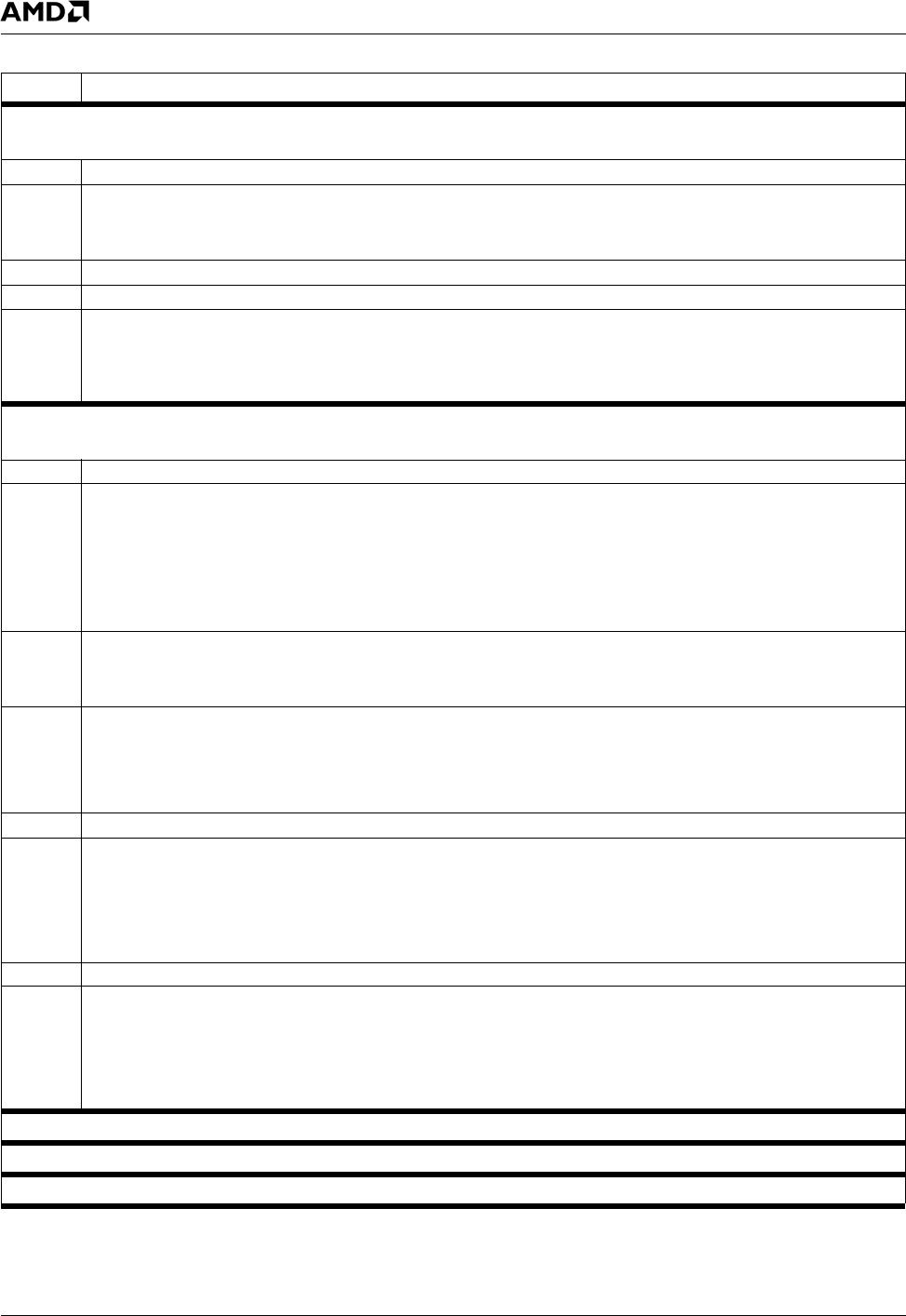

Video Processor Module - Video Processor Registers - Function 4

32581C

Offset 28h-2Bh Miscellaneous Register (R/W) Reset Value: 00001400h

Configuration and control register for miscellaneous characteristics of the Video Processor.

31:13 Reserved.

12 PLL2_PWR_EN (PLL2 Power-Down Enable).

0: Power-down.

1: Normal.

11:10 Reserved. Set to 1.

9:1 Reserved.

0 GAMMA_EN (Gamma Correction RAM Enable). Allows video or graphics (selected by F4BAR0+Memory Offset 04h[21])

to go to the Gamma Correction RAM.

0: Enable.

1: Disable.

Offset 2Ch-2Fh PLL2 Clock Select Register (R/W) Reset Value: 00000000h

Determines the characteristics of the integrated PLL2.

31:23 Reserved. Must be set to 0.

22:21 CLK_DIV_SEL (Clock Divider Select).

00: No division

01: Divide by 2

10: Divide by 4

11: Divide by 8

Divides the clock generated by the PLL2, using the programmed m (bits [14:8]) and n (bits [3:0]) values.

20 SEL_REG_CAL. Selects specific or previously-calculated values.

0: Values previously calculated from the CLK_SEL bits (bits [19:16]).

1: Values according to the m (bits [14:8]), n (bits [3:0]), and CLK_DIV_SEL (bits [22:21]) fields.

19:16 CLK_SEL (Clock Select). Selects frequency (in MHz) of the display clock.

0000: 25.175 0100: 50 1000: 65 1100: 108

0001: 31.5 0101: 49.5 1001: 75 1101: 135

0010: 36 0110: 56.25 1010: 78.5 1110: 27

0011: 40 0111: 44.9 1011: 94.5 1111: 24.923052

15 LFTC (Loop Filter Time Constant). This bit should be set when m (bits [14:8]) value is higher than 30.

14:8 m (Defines m PLL2 Value). Relevant when SEL_REG_CAL (bit 20) = 1. The following formula is used for calculating the

frequency using m and n values:

Fvco = OSCCLK * Km/Kn

Km = m + 1

Kn = n + 1

OSCCLK = 27 MHz

7:4 Reserved

3:0 n (Defines n PLL2 Value). Relevant when SEL_REG_CAL (bit 20) = 1. The following formula is used for calculating the fre-

quency using m and n values:

Fvco = OSCCLK * Km/Kn

Km = m + 1

Kn = n + 1

OSCCL = 27 MHz

Offset 30h-33h Reserved Reset Value: 00000000h

Offset 34h-37h Reserved Reset Value: 00000000h

Offset 38h-3Bh Reserved Reset Value: 00000000h

Table 7-7. F4BAR0+Memory Offset: Video Processor Configuration Registers (Continued)

Bit Description