AMD Geode™ SC3200 Processor Data Book 345

Video Processor Module - Video Processor Registers - Function 4

32581C

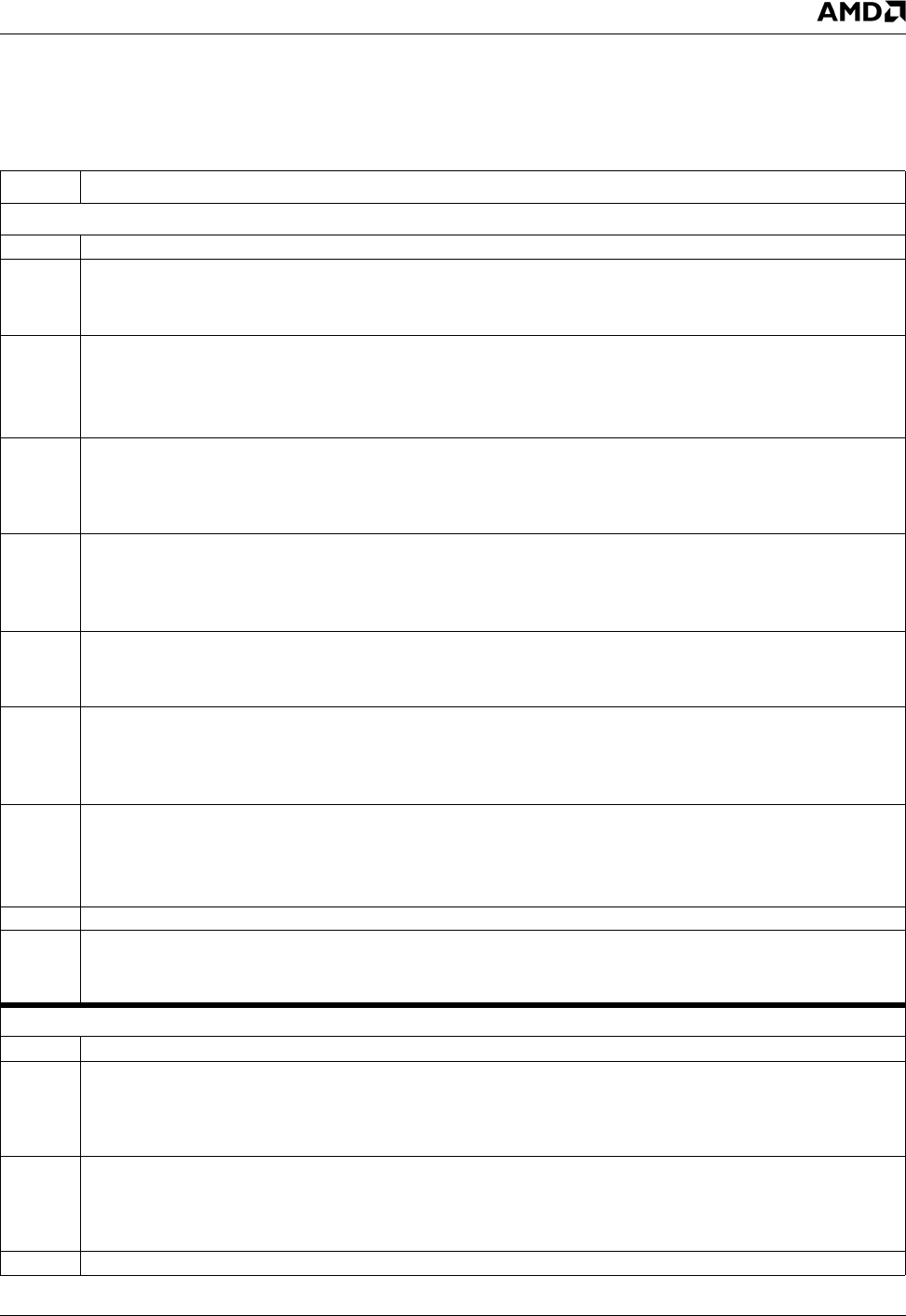

7.3.2.2 VIP Support Registers - F4BAR2

F4 Index 18h, Base Address Register 2 (F4BAR2) points to

the base address of where the VIP Configuration registers

are located. Table 7-8 shows the memory mapped VIP sup-

port registers accessed through F4BAR2.

Table 7-8. F4BAR2+Memory Offset: VIP Configuration Registers

Bit Description

Offset 00h-03h Video Interface Port Configuration Register (R/W) Reset Value: 00000000h

31:23 Reserved. Must be set to 0.

22 VIP FIFO Bus Request Threshold. VIP FIFO issues a bus request when it is filled with 32 or 64 bytes.

0: 64 bytes.

1: 32 bytes

21 VBI Task B Store to Memory. When this bit is enabled, raw VBI task B data is stored to memory.

0: Disable.

1: Enable.

This bit is relevant only if bit 18 (VBI Configuration Override) = 1 (enabled).

20 VBI Task A Store to Memory. When this bit is enabled, raw VBI task A data is stored to memory.

0: Disable.

1: Enable.

This bit is relevant only if bit 18 (VBI Configuration Override) = 1 (enabled).

19 VBI Ancillary Store to Memory. When this bit is enabled, raw VBI Ancillary data is stored to memory.

0: Disable.

1: Enable.

This bit is relevant only if bit 18 (VBI Configuration Override) = 1 (enabled).

18 VBI Configuration Override. When this bit is enabled, bits [21:19] override the setup specified in bits 17 and 16.

0: Disable.

1: Enable.

17 VBI Data Task. Specifies the CCIR656 video stream task used to store raw VBI data to memory.

0: Task B.

1: Task A.

This bit is relevant only if bit 16 (VBI Mode for CCIR656) = 1 and bit 18 (VBI Configuration Override) = 0 (disabled).

16 VBI Mode for CCIR656. Specifies the mode in which to store VBI data to memory.

0: Use CCIR656 ancillary data to store VBI data to memory.

1: Use CCIR656 video task A or B to store VBI data to memory, depending on the value of bit 17 (VBI Data Task).

This bit is only used if bit 18 (VBI Configuration Override) = 0 (disabled).

15:2 Reserved. Set to 0.

1:0 Video Input Port Mode. Selects VIP operating mode.

10: CCIR656 mode.

All other decodes: Reserved.

Offset 04h-07h Video Interface Control Register (R/W) Reset Value: 00000000h

31:18 Reserved. Must be set to 0.

17 Line Interrupt. When asserted, allows interrupt (INTC#) generation when the Video Current Line register (F4BAR2+ Mem-

ory Offset 10h) contents equal the Video Line Target Register (F4BAR2+ Memory Offset 14h) contents.

0: Disable.

1: Enable.

16 Field Interrupt. When asserted, allows interrupt (INTC#) generation at the end of a field (i.e., the end of active video for the

current field). Interrupt generation can be enabled regardless of whether or not video capture (store to memory) is enabled.

0: Disable.

1: Enable.

15:11 Reserved. Must be set to 0.